国際特許分類[H01L27/105]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969)

国際特許分類[H01L27/105]の下位に属する分類

ダイナミックランダムアクセスメモリ構造 (2,482)

スタティックランダムアクセスメモリ構造 (855)

リードオンリーメモリ構造 (4,422)

国際特許分類[H01L27/105]に分類される特許

41 - 50 / 4,210

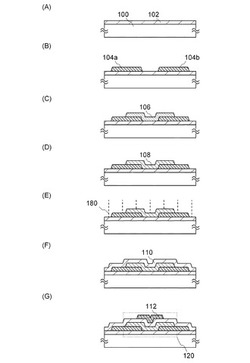

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

最適化された信頼性を有する自己参照MRAMセル

【課題】MRAMセルに比べてより高い温度で確実に書き込まれ得る熱アシストされた書き込み操作と自己参照読み出し操作とに適した磁気ランダムアクセスメモリ(MRAM)セルを提供する。

【解決手段】メモリセルは、第1部分2’と第2部分2”とを有する磁気トンネル接合部分から構成され、各部分が、記憶層23,24とセンス層21,22とトンネル障壁層25,26とから構成され、この磁気トンネル接合が、当該2つの記憶層との間に反強磁性層20をさらに有し、これらの記憶層の各々の記憶磁化方向を臨界温度未満でピン止めし、これらの記憶磁化方向を臨界温度以上で自由にする。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

半導体記憶装置の製造方法及び半導体記憶装置

【課題】抵抗変化膜の抵抗変化を容易にする半導体記憶装置の製造方法及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置の製造方法は、金属酸化物を含む抵抗変化膜との接触対象層にハロゲンを導入する工程と、前記ハロゲンを熱処理により前記接触対象層から前記抵抗変化膜に拡散させる工程とを備えている。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

磁気メモリの製造装置

【課題】より小さい磁場で磁性層の磁化方向を所定の方向に設定する。

【解決手段】磁気メモリ21の磁場印加装置30は、磁気メモリ21の磁性層に磁場を印加し、磁性層の磁化方向を初期化する磁石32A及び32Bと、磁性層に磁場が印加されている間に、磁気メモリ21の温度を上昇させる温度上昇機構33と、制御回路34とを含む。磁石32A及び32Bはそれぞれ、設定する磁化方向に応じて、磁場を発生し、磁気メモリ21の上から下へ向かう磁場、又は下から上へ向かう磁場が印加される。

(もっと読む)

半導体記憶装置

【課題】データ書き込みエラー発生と消費電力を低減させた半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る半導体記憶装置は、第1極性の電圧パルス印加によってメモリセルに第1動作及び第2動作をさせるユニポーラ方式、並びに、第1極性とは異なる第2極性の電圧パルス印加によってメモリセルに第1動作をさせ且つ第1極性の電圧パルス印加によってメモリセルに第2動作をさせるバイポーラ方式の動作モードを有するデータ書き込み部と、メモリセルの第1動作の回数をカウントする第1動作回数カウント回路と、第1動作回数カウント回路を参照し、ユニポーラ方式による第1動作回数が第1規定回数に達した場合にデータ書き込み部の動作モードをバイポーラ方式に切り替える動作モード切り替え部とを備える。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

41 - 50 / 4,210

[ Back to top ]