国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

201 - 210 / 855

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

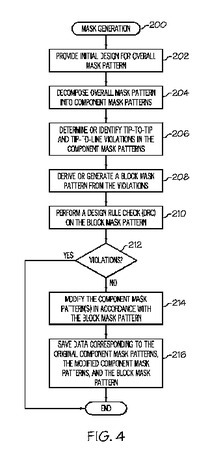

設計規則違反を低減するために多重露光及び遮断マスクの手法を用いる半導体デバイス製造

【解決手段】

半導体デバイス(400)を製造する方法は、半導体材質(402)の層及び半導体材質(402)の層の上の絶縁材質(404)の層を備える基板上に、ハードマスク材質(408)の層が絶縁材質(404)の層の上になるように、ハードマスク材質(408)の層を形成することによって開始する。多重露光フォトリソグラフィ手順が実行されて、ハードマスク材質(408)の層の上にフォトレジスト特徴部の結合されたパターンが作製され、またフォトレジスト特徴部の結合されたパターンを用いてハードマスク材質内に凹部線パターンが作製される。方法は、凹部線パターン(422)の指定された区画をフォトレジスト特徴部の遮断パターン(442)で覆い、そして溝(452)のパターンを絶縁材質(404)内に形成することによって継続し、ここで溝(452)のパターンは、フォトレジスト特徴部の遮断パターン(442)及びハードマスク材質(408)によって規定される。その後、電気伝導材質(472)が溝(452)内に堆積させられて、半導体デバイスのための導電線がもたらされる。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】回路構成を複雑化することなくソフトエラー低減化を図ったメモリセル構造を有する半導体記憶装置を得る。

【解決手段】NMOSトランジスタN1及びPMOSトランジスタP1によるインバータI1(出力部が記憶端子Na)とNMOSトランジスタN2及びPMOSトランジスタP2によるインバータI2(出力部が記憶端子Nb)とが交叉接続され、さらにNMOSトランジスタN3及びN4が記憶端子Na及びNbにそれぞれ接続される。記憶端子Naに一方電極が接続されるNMOSトランジスタN1及びN3はPウエル領域PW0及びPW1に分けて形成されるともに、記憶端子Nbに一方電極が接続されるNMOSトランジスタN2及びN4はPウエル領域PW1及びPW0に分けて形成される。Pウエル領域PW0及びPW1はNウエル領域NWを挟んで各々反対側に形成される。

(もっと読む)

半導体装置

【課題】CAMにおけるメモリセル面積の縮小化を図る。

【解決手段】データ線(D0,D1)を第1記憶部(MA)及び第2記憶部(MB)とで共有し、また、第1比較データ線(CD0)に結合された第1トランジスタ(MC0)と、第1記憶部の記憶ノードに結合された第2トランジスタ(MCA)とを直列接続して第1比較回路(11)を形成し、第2比較データ線(CD1)に結合された第3トランジスタ(MC1)と、上記第2記憶部の記憶ノードに結合された第4トランジスタ(MCB)とを直列接続して第2比較回路(12)を形成することは、拡散層や配線層のレイアウトにおける対称性を向上させ、メモリセルをその中心を通る中心線に対して線対称となるレイアウトの容易化を達成する。それにより製造プロセス条件を最適化し易くなり、製造プロセスのばらつきが低減されてメモリセルの微細化が達成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】基板の内部であって、活性領域と素子分離領域との境界領域にコンタクトホールが形成された場合に、基板に流れるリーク電流を抑制できるようにする。

【解決手段】半導体基板10の上部に形成された素子分離領域10a及び活性領域10bと、半導体基板10の上に形成された絶縁膜12と、絶縁膜12に少なくとも活性領域10bを露出するように形成され、且つ、素子分離領域10aにおける活性領域10bとの境界領域を含む領域に形成されたコンタクトホール13と、コンタクトホール13における、活性領域10bの上に位置する第1の底面の上に形成された第1のバリアメタル膜14と、コンタクトホール13における、最下端に位置する第2の底面と第1の底面とをつなぐ壁面上に形成された第2のバリアメタル膜17とを備える。第2のバリアメタル膜17は、第1のバリアメタル膜14よりも比抵抗が高いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】n型MISトランジスタを有する半導体装置の特性ばらつきを低減させる。

【解決手段】シリコン基板1上のメモリ領域RMに形成された、n型導電型である第1トランジスタQ1は、ホウ素を含むメモリ用チャネル領域CH1と、メモリ用ゲート電極GE1の両側壁側下に形成された、n型のメモリ用エクステンション領域ET1および酸素を含む拡散防止領域PA1とを有している。ここで、拡散防止領域PA1はメモリ用エクステンション領域ET1を内包するようにして形成されている。また、拡散防止領域PA1は、少なくともその一部が、メモリ用エクステンション領域ET1とメモリ用チャネル領域CH1との間に配置されている。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、I/O構成の切り替えを容易とする。

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、外部との間で同時に入出力する単位外部データのビット数が可変であり、チップ識別情報LIDと比較するためのチップ選択情報SELを、単位外部データのビット数に応じて可変とする。これにより、I/O構成の変更に伴うページ構成の切り替えを不要とすることが可能となる。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

201 - 210 / 855

[ Back to top ]