国際特許分類[H01L29/417]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475) | 整流,増幅またはスイッチされる電流を流すもの (1,983)

国際特許分類[H01L29/417]に分類される特許

101 - 110 / 1,983

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の酸素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

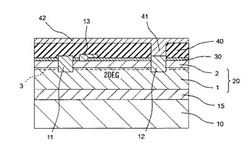

半導体装置の製造方法

【課題】設計された形状およびサイズのゲート電極を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体層12の表面上のうち、互いに離間した位置に、チタン層17a、18a、アルミニウム層17b、18b、ニッケル層17c、18c、金層17d、18dがこの順で積層した積層体17、18を形成し、これらを、アルミニウムの融点より高い温度で加熱して複数の金属体17´、18´を形成するするとともに、これらの複数の金属体17´、18´を半導体層12にオーミック接触させる。この後、複数の金属体17´、18´を薄膜化して複数の合金層13a、14aを形成し、合金層13a、14aを含むドレイン電極13およびソース電極14を形成する。次に、ドレイン電極13とソース電極14との間のレジスト層19に開口部20し、この開口部20内にゲート電極15を形成する。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】ソース電極およびドレイン電極と有機半導体層とにおける電荷注入効率の向上と性能の確保とを両立させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含む金属含有材料により形成された有機半導体層と、互いに離間されたソース電極およびドレイン電極と、有機半導体層とソース電極およびドレイン電極とが重なる領域において有機半導体層とソース電極およびドレイン電極との間に挿入され、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含まない非金属含有材料により形成された有機導電層とを備える。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

窒化物半導体層のエッチング方法及びこれを用いた窒化物半導体装置の製造方法

【課題】高抵抗なダメージ層を形成しない窒化物半導体層のエッチング方法と、これを用いた低抵抗なオーミック電極を備える窒化物半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の窒化物半導体層のエッチング方法は、(a)窒化物半導体層に不純物イオンを注入し、その表面から所定深さまで不純物領域を形成する工程と、(b)前記不純物領域を熱処理する工程と、(c)前記不純物領域の前記表面側の所定領域をウェットエッチングで除去する工程とを備える。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置およびその作製方法

【課題】In−Sn−Zn−O系半導体を用いた半導体装置を作製する際の加工技術を確立する。

【解決手段】Cl2または、BCl3または、SiCl4などの塩素を含むガスを用いたドライエッチングによりIn−Sn−Zn−O系半導体層を選択的にエッチングする。In−Sn−Zn−O系半導体層上に接して形成する導電層を選択的に除去してソース電極層及びドレイン電極層を形成する場合、塩素を含むガスに加えて酸素を含むガス、またはフッ素を含むガスを用い、In−Sn−Zn−O系半導体層がほとんど除去されないように導電層を選択的にエッチングすることができる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

101 - 110 / 1,983

[ Back to top ]