国際特許分類[H01L29/417]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475) | 整流,増幅またはスイッチされる電流を流すもの (1,983)

国際特許分類[H01L29/417]に分類される特許

81 - 90 / 1,983

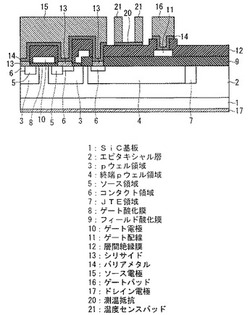

炭化珪素半導体装置

【課題】少ない工程数で形成でき、耐熱性に優れた温度検出素子を備える炭化珪素(SiC)半導体装置を提供する。

【解決手段】SiC半導体装置は、SiC基板1に形成された半導体素子と、底面にバリアメタル14を備える配線層を用いて形成したソース電極15およびゲートパッド16と、その配線層のバリアメタル14の一部を用いて形成した測温抵抗体20を備える。

(もっと読む)

半導体装置の製造方法

【課題】二酸化珪素からなる層間絶縁膜を挟んでアルミニウムを含む電極とゲート電極とを配置した場合に、当該アルミニウムを含む電極とゲート電極とが短絡することを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】MOSFET100の製造方法は、活性層7上にゲート酸化膜91を形成する工程と、ゲート酸化膜91上にゲート電極93を形成する工程と、活性層7に対してオーミック接触するソースコンタクト電極92を形成する工程と、ソースコンタクト電極92が形成された後、ゲート電極93を覆うように二酸化珪素からなる層間絶縁膜94を形成する工程とを備え、ソースコンタクト電極92を形成する工程は、活性層7に接触するようにアルミニウムを含む金属層を形成する工程と、金属層を合金化する工程とを含む。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

グラフェンの合成方法並びに半導体装置及びその製造方法

【課題】触媒金属膜の任意の領域にグラフェンを選択的に合成しうるグラフェンの合成方法を提供する。

【解決手段】基板の所定の領域上に、触媒金属膜を形成する。次いで、触媒金属膜の側面に、触媒金属膜よりも触媒能の低い被覆膜を形成する。次いで、触媒金属膜の上面上に、触媒金属膜を触媒としてグラフェンを選択的に合成し、グラフェンチャネルを形成する。次いで、基板上に、グラフェンチャネルに接合されたソース電極及びドレイン電極を形成する。次いで、触媒金属膜及び被覆膜を除去する。次いで、グラフェンチャネル上に、ゲート絶縁膜及びゲート電極を形成する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置の製造方法

【課題】レーザアニールによって金属シリサイド膜を形成する工程を含む半導体装置の製造方法において、金属シリサイド膜を形成する領域以外の領域に加わる熱負荷を低減して、半導体装置の特性劣化を抑制できる技術を提供する。

【解決手段】本発明では、例えば、シリサイド化する領域(領域AR1)に透過膜PFを形成し、シリサイド化しない領域(領域AR2)に透過膜PFを形成しないことにより、紫外線レーザ光UVを照射した際、シリサイド化する領域の温度をシリサイド化するための共晶化温度よりも高くする一方、シリサイド化しない領域の温度をシリサイド化するための共晶化温度よりも低くする。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

81 - 90 / 1,983

[ Back to top ]