国際特許分類[H01L29/417]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475) | 整流,増幅またはスイッチされる電流を流すもの (1,983)

国際特許分類[H01L29/417]に分類される特許

71 - 80 / 1,983

半導体装置

【課題】大電力用途の半導体装置に用いるトランジスタには、高いドレイン電流を確保するためのチャネル領域を有する構造が必要である。その一例のトランジスタとして、縦型(トレンチ型)トランジスタも検討されているが、ドレイン電流のオンオフ比がとれず、良好なトランジスタ特性が得られないという課題がある。

【解決手段】導電性を有する基板上において、側面がテーパー形状の断面を有する複数の島状の領域が表面にドット状に設けられた酸化物半導体層を、基板と酸化物半導体層の間に設けられた第1の電極と酸化物半導体層上に設けられた第2の電極とで挟持し、絶縁層を介した酸化物半導体層の島状の領域の側面上に、ゲート電極としての機能を有する導電層を設ける。

(もっと読む)

薄膜デバイス及びその製造方法

【課題】酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上のインジウムを含む酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分の表面層15におけるXPSスペクトルのインジウム3d軌道起因のピーク位置が、表面層15の下部に存在する酸化物半導体領域におけるXPSスペクトルのインジウム3d軌道起因のピーク位置よりも、高エネルギ側にシフトしている。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

GaN系化合物半導体装置

【課題】ゲート電極へのリーク電流を大幅に低減できるGaN系化合物半導体装置を提供する。

【解決手段】このGaN系HFETによれば、ゲート電極をなすTiN膜の抵抗率(Ω・μm)を24.7(Ω・μm)とした。このように、ゲート電極のショットキー電極層としてのTiN膜の抵抗率が10Ωμm以上であることによって、ゲート電極をなす金属材料TiNの抵抗率(ゲートメタル抵抗率)が10Ωμm未満である場合に比べて、ゲートリーク電流を著しく低減できる。

(もっと読む)

有機トランジスタ及びその製造方法

【課題】ソース、ドレイン電極と有機半導体層の間の接触抵抗を低減して、短チャネル化により高速応答性能を向上させ、かつ、短チャネル化に伴うソース、ドレイン電極とゲート電極間の短絡の発生を回避可能とする。

【解決手段】絶縁性の基板と、基板上に相互間に間隔を設けて配置され、各々台状平面を形成する一対の絶縁性の台座2、3と、一方の台座が形成する台状平面上に設けられたソース電極4と、他方の台座が形成する台状平面上に設けられたドレイン電極5と、一対の台座の間の基板上に設けられたゲート電極6と、ソース電極及びドレイン電極の上面に接触させて配置された有機半導体層7とを備える。ゲート電極と有機半導体層の下面とはギャップ領域8を介在させて上下方向に対向し、ギャップ領域に面する台座の側面は、上側端縁に対して下側端縁がゲート電極から遠ざかる側に後退した形状を有する。

(もっと読む)

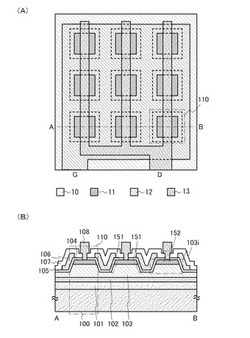

薄膜トランジスタおよびその製造方法、電子機器

【課題】コンパクトでありながら、より安定した動作を行う薄膜トランジスタを提供する。

【解決手段】この薄膜トランジスタは、ゲート電極と、絶縁膜を介してゲート電極と対向して配置された有機半導体層と、この有機半導体層の上に設けられた絶縁性構造体と、互いに離間して配置され、かつ、有機半導体層の上面の一部とそれぞれ接するソース電極およびドレイン電極と、絶縁性構造体を覆い、ソース電極と接続されると共にドレイン電極と分離された導電性材料層とを有する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】酸化物半導体を使用する薄膜トランジスタの特性を向上させることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ表示板を提供する。本発明の一実施形態に係る薄膜トランジスタ表示板は、基板の上に配置するゲート配線層、前記ゲート配線層の上に配置する酸化物半導体層、及び前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、前記データ配線層は銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む。

(もっと読む)

半導体素子およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体素子およびその製造方法等を提供する。

【解決手段】半導体素子は、有機半導体層と、この有機半導体層と接するように配設された電極と、この電極とは別体として形成され、かつ電極と電気的に接続された配線層とを備えている。半導体素子の製造方法は、基板上に、有機半導体層およびこの有機半導体層と接する電極を形成する工程と、この電極と電気的に接続された配線層を形成する工程とを含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】エピ基板を用いずに形成可能な半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は,シリコン基板と,半導体素子と,高濃度層と,ニッケルシリサイド層と,金属層と,を具備する。シリコン基板は,互いに対向する第1,第2の主面を有し,第1導電型の不純物を第1の濃度含有する。MOS型半導体構造は,第1の主面側に配置される。高濃度層は,第2の主面側に配置され,前記不純物を前記第1の濃度より大きい第2の濃度含有する。ニッケルシリサイド層は,前記高濃度層上に配置され,硫黄又はアンチモンを含む。金属層は,ニッケルシリサイド層上に配置される。

(もっと読む)

窒化物半導体装置

【課題】リードフレーム上に搭載された窒化物FETを備えスイッチング特性に優れた窒化物半導体装置を提供する。

【解決手段】窒化物FETと、複数のリードを含むリードフレームと、を備え、前記窒化物FETは少なくとも第1の主電極と第2の主電極と制御電極とを有し、前記リードフレームは、前記第1の主電極に接続される第1のリードと、前記第2の主電極に接続される第2のリード及び第3のリードと、前記制御電極に接続される第4のリードと、を有し、前記窒化物FETは、前記第3のリードと前記第4のリードとの間に印加される電圧に応じて前記第1のリードと前記第2のリードとの間に電流を流すことを特徴とする窒化物半導体装置。

(もっと読む)

71 - 80 / 1,983

[ Back to top ]