国際特許分類[H01L29/417]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475) | 整流,増幅またはスイッチされる電流を流すもの (1,983)

国際特許分類[H01L29/417]に分類される特許

31 - 40 / 1,983

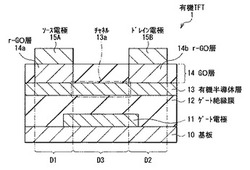

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法および表示装置

【課題】ソースおよびドレインと半導体層との間において良好なコンタクトを確保することが可能な有機薄膜トランジスタを提供する。

【解決手段】有機薄膜トランジスタは、有機材料よりなる半導体層上のソース電極およびドレイン電極に対向する第1および第2の領域のそれぞれに導電層を有し、この導電層が、還元反応によって導電性が変化する酸化物を含むものである。導電層が、半導体層とソース電極およびドレイン電極とのコンタクト層として機能すると共に、トップコンタクト構造では、製造プロセスにおいて半導体層上に、上記導電層を含むエッチングストッパ層を形成可能となる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】低コンタクト抵抗を実現し得る半導体基板上の半導体層と電極配線層とのオーミック電極構造を提供する。

【解決手段】半導体基板106と、半導体基板106上に形成された第1のバリア層107と、第1のバリア層107上に形成された厚さ1nm以上40nm以下のチャネル層108と、チャネル層108の上に形成された第2のバリア層102と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第1の電極領域109と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第2の電極領域109とを備える半導体装置であって、少なくとも第1の電極領域109は、チャネル層108と接触する側の面が凹凸形状で構成されている。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

31 - 40 / 1,983

[ Back to top ]