国際特許分類[H01L29/744]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586) | サイリスタ型装置,例.4層再生作用をもつもの (302) | ゲートターンオフサイリスタ (51)

国際特許分類[H01L29/744]の下位に属する分類

電界効果によりターンオフするもの

国際特許分類[H01L29/744]に分類される特許

41 - 50 / 51

半導体装置及びその製造方法、この半導体装置を用いた電力変換装置

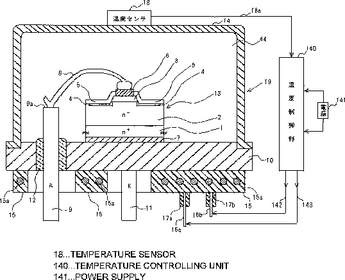

可制御電流が大きく、かつ低損失のパワー半導体装置を得るために、ワイドギャップ半導体を用いるバイポーラ半導体素子の温度を、ヒーターなどの加熱手段を用いて上昇させる。その温度は、ワイドギャップバイポーラ半導体素子の、温度の上昇に応じて低下するビルトイン電圧の低下量に対応する前記ワイドギャップバイポーラ半導体素子の定常損失の減少量が、前記温度の上昇に応じて増加するオン抵抗の増加量に対応する前記定常損失の増加量よりも大きくなる温度を超える温度にする。  (もっと読む)

(もっと読む)

高耐熱半導体装置

150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得るために、ワイドギャップ半導体素子の外面を合成高分子化合物で被覆する前記合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAと、シロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。  (もっと読む)

(もっと読む)

高耐熱合成高分子化合物及びこれで被覆した高耐電圧半導体装置

【課題】150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得る。

【解決手段】ワイドギャップ半導体素子の外面を、合成高分子化合物で被覆する。この合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAとシロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。この合成高分子化合物に高い熱伝導性を有する絶縁性セラミックスの微粒子を混合し、熱伝導率を高くしている。

(もっと読む)

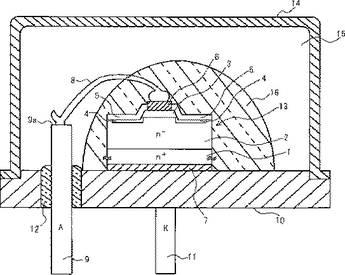

電力用半導体装置

【課題】リカバリー損失の低減を図るべく、アノード電極領域の不純物拡散深さを浅くすることができる電力用半導体装置を提供することを目的とする。

【解決手段】半導体基板1、ゲート電極領域(制御電極領域)2、カソード電極領域(第一の主電極領域)3、アノード電極領域(第二の主電極領域)4、およびガードリング5を備えている。半導体基板1は、断面視において、主面に対して略垂直に形成されている垂直部1aと、垂直部1aと接続するメサ部1bとを有する側面部を有している。ゲート電極領域2は、半導体基板1の第一の主面1c内に形成されている。カソード電極領域3は、ゲート電極領域2の表面内の一部に形成されている。アノード電極領域4は、半導体基板1の第二の主面1d内に形成されている。ガードリング5は、半導体基板1の第二の主面1d内に形成されており、アノード電極領域4を環状に取り囲んでいる。

(もっと読む)

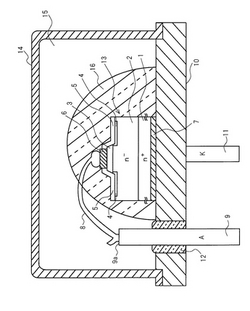

ゲートターンオフサイリスタ

メサ型のワイドギャップ半導体ゲートターンオフサイリスタでは、ゲートの耐電圧が低く、またリーク電流が大きい。高温時にはp型不純物のイオン化率が室温に比べ大幅に増大するため、ホールの注入量が増えるとともに少数キャリアのライフタイムも伸びるため、最大可制御電流が室温に比べ大幅に低下する。その点を解決するために、一方の面にカソード電極を有するn型SiCのカソードエミッタ層の上にp型ベース層を設け、p型ベース層の上に薄いn型ベース層を設ける。n型ベース層の中央部にメサ型のp型アノードエミッタ層を設け、n型ゲートコンタクト領域をp型アノードエミッタ層とn型ベース層の接合部から十分離して設けるとともに、n型低抵抗ゲート領域をn型ベース層内にアノードエミッタ層を取り囲むように設ける。  (もっと読む)

(もっと読む)

半導体装置

【課題】pin構造を有する半導体装置のオン電圧を小さくする。

【解決手段】pin構造を有する半導体装置において、p層102とn-型半導体基板101との間のpn接合に逆バイアスを印加して生じる空乏層が伸びる範囲での、p層102の不純物量に対するn-型半導体基板101の不純物量の比を2/3以下とする。これにより半導体装置の厚さを薄くすることができるので、オン電圧を小さくすることができる。

(もっと読む)

パワー半導体素子

【課題】通電電流を検出用コイルや検出用抵抗を用いずに検出する、小型、軽量、高速かつ低損失のパワー半導体素子回路を構成するのに適したパワー半導体素子を提供すること。

【解決手段】本発明のパワー半導体素子は、実質的に同じバンドギャップを有するワイドギャップ半導体材料からなるp型層34とn型層33,35とが少なくとも三層交互に、複数層積層されたバイポーラ型のパワー半導体素子である。複数層33,34,35のうち中間に挟まれた層34に電気的に接続され、この素子を通して流れる通電電流を制御する制御端子16Aを備える。複数層33,34,35のうち少なくとも一層、例えば層34に、通電電流に応じて光を発生する再結合センターが含まれ、この再結合センターで発生した光が外部へ放射されるようになっている。

(もっと読む)

光結合パワー半導体素子

【課題】小型、軽量、高速かつ低損失のパワー半導体素子回路を構成するのに適した光結合パワー半導体素子を提供すること。

【解決手段】本発明の光結合パワー半導体素子は、実質的に同じバンドギャップを有するワイドギャップ半導体材料からなるp型層34とn型層33,35とが少なくとも三層交互に、複数層積層されたバイポーラ型のパワー半導体素子と、受光素子とを含む。パワー半導体素子は、複数層33,34,35のうち中間に挟まれた層34に通電電流を制御する制御端子16Aを備える。複数層33,34,35のうち少なくとも一層、例えば層34に、通電電流に応じて光を発生する再結合センターが含まれ、この再結合センターで発生した光が外部へ放射されるようになっている。受光素子は、その光を受けて、パワー半導体素子の通電電流に応じた出力を発生する。

(もっと読む)

半導体装置及びそのパッケージ構造並びに電力変換装置

半導体装置及びそのパッケージ構造並びに電力変換装置

【目的】オン電圧の増大などの悪影響を招くことなくゲートから離れた領域に配置されたユニットをターンオフしやすくするパッケージ構造を提案する。

【構成】補助カソードリード24をペレット10のゲート圧接部33から最も離れた領域に配置された単位素子に接する部分のカソードバッファ32電極に接触させ、ターンオフ時の補助カソード電流の押し込み効果が顕著になるようにする。

【効果】遮断耐量を高めることができ、素子の大電流化によるペレット直径の増大への対応が容易になる。さらにGTO素子の保護回路であるスナバ回路のコンデンサを小さくでき、スナバの損失を小さくできる。

(もっと読む)

41 - 50 / 51

[ Back to top ]