国際特許分類[H01L29/744]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586) | サイリスタ型装置,例.4層再生作用をもつもの (302) | ゲートターンオフサイリスタ (51)

国際特許分類[H01L29/744]の下位に属する分類

電界効果によりターンオフするもの

国際特許分類[H01L29/744]に分類される特許

21 - 30 / 51

電力半導体デバイスのためのメサ終端構造とメサ終端構造をもつ電力半導体デバイスを形成するための方法

【課題】デバイスのピーク電界強度が低減し、実効的降服電圧を増加させ、デバイスの歩留まりを改善すること。

【解決手段】第1の伝導型を有するドリフト層と、前記ドリフト層上にあって、前記第1の伝導型とは反対の第2の伝導型を有し、前記ドリフト層とP−N接合を形成するバッファ層と、前記P−N接合の近傍の前記ドリフト層内にあって前記第2の伝導型を有する接合終端拡張領域とを含む電子デバイスを提供する。前記バッファ層は、前記接合終端拡張領域の埋め込み部分上を延びる階段部分を含む。関連する方法も開示される。

(もっと読む)

高性能シリコンパワーデバイスにおける不均一少数キャリア寿命分布

【課題】単結晶シリコンセグメントを熱処理することによって、少数キャリア再結合中心の所望のプロファイルを有するセグメント、並びにそのようなセグメントを製造する方法の提供。

【解決手段】セグメントは前表面と、後表面と、前表面と後表面の間にある中央平面を有する。本発明の方法では、セグメントは結晶格子空孔を形成するために熱処理に付され、空孔はシリコンのバルクに形成される。セグメントはその後、中央平面にあるいは中央平面の近くにピーク密度があり、濃度がセグメントの前表面の方向にほぼ減少していく空孔濃度プロファイルを有するセグメントを製造するために、前表面に拡散する結晶格子空孔のすべてではないが、いくつかを許容する速度で熱処理の温度から冷却される。白金原子はその後に、結果的に生じる白金濃度プロファイルが実質的に結晶格子空孔の濃度プロファイルに関連するようにシリコンマトリックスのなかに内方拡散される。

(もっと読む)

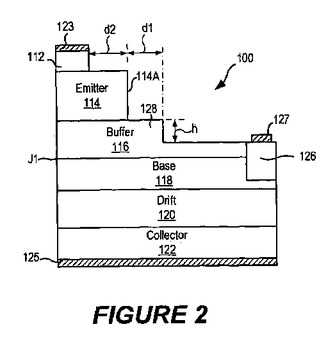

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

ゲートターンオフサイリスタ

【課題】メサ型のエミッタ層を有するワイドギャップ半導体のゲートターンオフサイリスタにおいて、可制御電流を大きくできるものを提供すること。

【解決手段】 n型の第1のエミッタ層、p型の第1のベース層、n型の第2のベース層、p型の第2のエミッタ層をこの順に備える。第2のベース層の表面近傍の、メサ型の第2エミッタ層と第2のベース層との接合部近傍を含むメサの底部に、p型の領域7を介在させてn型の低抵抗ゲート領域5を設ける。これにより、エミッタ層と、そのエミッタ層に近接する、ゲートが設けられるベース層との接合部の端部近傍の絶縁膜の電界を緩和する。なお、各層および各領域のn型とp型とを入れ替えても良い。

(もっと読む)

半導体装置及びその駆動方法

【課題】ターンオフ時間を短くできるサイリスタを有する半導体装置を提供する。

【解決手段】基板に第1導電型の第1半導体領域が形成され、その表層部に第2導電型の第2半導体領域と第2導電型の第3半導体領域(アノードAN)と第1導電型の第4半導体領域(アノードゲートAG)が、第2半導体領域の表層部に第1導電型の第5半導体領域(カソードCA)と第2導電型の第6半導体領域(カソードゲートCG)が形成され、第1及び第2半導体領域の境界から第2及び第5半導体領域の境界までの領域の第2半導体領域上にゲート絶縁膜及びゲート電極MGが、第3半導体領域に負荷素子が形成されてサイリスタSCRが構成された半導体装置において、サイリスタをオンからオフにする際に、アノードより高電位をアノードゲートに印加し、アノードとアノードゲートでサイリスタ内部に構成されるダイオードを降伏させてアノードの電位を制御して駆動する。

(もっと読む)

炭化珪素バイポーラ型半導体装置

【課題】メサ構造をもつ炭化珪素バイポーラ型半導体装置において、素子の表面付近に存在する欠陥核を起点とした積層欠陥の発生およびその面積拡大を抑制し、これにより順方向電圧の増加を抑制する。

【解決手段】第1導電型炭化珪素単結晶基板、第1導電型炭化珪素ドリフト層、第2導電型炭化珪素電荷注入層および該炭化珪素電荷注入層よりもドーピング密度が高い第2導電型の高ドーピング層が、この順序にて積層してなり、前記炭化珪素ドリフト層から前記高ドーピング層側の素子表面に至るメサ構造を有し、前記高ドーピング層の厚さが15nm〜1.5μmであり、かつ、前記高ドーピング層における最大ドーピング密度が1×1020cm-3〜2×1021cm-3であることを特徴とする炭化珪素バイポーラ型半導体装置。

(もっと読む)

pnダイオード、電気回路装置、および電力変換装置

【課題】小型,安価でオン抵抗の大きなpnダイオードを提供する。

【解決手段】このSiCpnダイオードは、約3×1013cm−2以上の電子線を照射したことで、ライフタイム制御がなされている。このライフタイム制御の結果、図1の電流電圧特性K10に示すように、このSiCpnダイオードでは、電流は約32Vから流れ出し、100A通電時のオン電圧は50Vとなった。このときの上記SiCpnダイオードのオン時の抵抗は0.5Ωである。このSiCpnダイオードの通電領域は0.4cm2であり、上記ライフタイム制御によってオン抵抗を増大させて、0.2Ωcm2にしたから、例えば、従来はダイオードと抵抗とを直列に接続して使用していた電気回路装置において、上記抵抗を省略可能となる。

(もっと読む)

半導体装置

【課題】可制御電流が大きく、低損失のパワー半導体装置に適したアセンブリ構造を提供すること。

【解決手段】金属基板125と、絶縁板126と、金属膜7とを備える。金属基板125上に、ワイドギャップ半導体層からなるバイポーラスイッチング素子20を備える。金属膜7上に、n型ワイドギャップ半導体層を含むダイオード素子13を備える。バイポーラスイッチング素子20の低電位側の主電極32は、金属基板125に直接に半田付けされている。一方、バイポーラスイッチング素子20の高電位側の主電極29は、金属膜7に配線34、7aを介して電気的に接続されている。ダイオード素子13の低電位側の主電極32は、金属膜7に直接に半田付けされている。一方、ダイオード素子13の高電位側の主電極6は、金属基板125に配線8を介して電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】可制御電流が大きく、低損失のパワー半導体装置を作製すること。

【解決手段】順方向特性にビルトイン電圧を有するワイドギャップバイポーラ半導体素子を形成するように、互いに異なる導電型を有する少なくとも2層のワイドギャップ半導体層1、2、3を積層する。積層欠陥を有するワイドギャップ半導体層1、2、3に、所定の照射エネルギーのγ線、電子線または荷電粒子線を所定量照射する。

(もっと読む)

半導体装置及びその製造方法、動作方法、この半導体装置を用いた電力変換装置

【課題】可制御電流が大きく、かつ低損失のパワー半導体装置を得ること。

【解決手段】ワイドギャップ半導体を用いた、順方向特性にビルドイン電圧を有するワイドギャップバイポーラ半導体素子13を備える。ワイドギャップバイポーラ半導体素子13を収納し、ワイドギャップバイポーラ半導体素子13を外部の装置に接続するための電気接続手段7、8、9、11を有する半導体パッケージ10、14を備える。半導体パッケージ10、14内の前記ワイドギャップバイポーラ半導体素子13を50℃以上、750℃以下の温度範囲に加熱するための発熱手段15を備える。

(もっと読む)

21 - 30 / 51

[ Back to top ]