国際特許分類[H01L29/786]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 薄膜トランジスタ (12,139)

国際特許分類[H01L29/786]に分類される特許

71 - 80 / 12,139

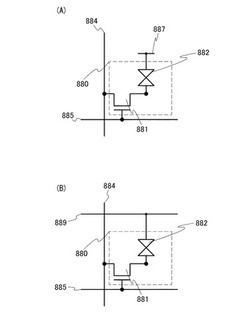

半導体装置

【課題】酸化物半導体を用いたトランジスタを具備する画素において、開口率の向上を図る。

【解決手段】酸化物半導体を用いたトランジスタ881は、リーク電流が小さいため、画素880内の容量素子を設ける必要がなくなる。または容量素子を小さくすることができ、たとえば液晶容量よりも小さくすることができる。これらによって、画素880の開口率を向上することができる。前記トランジスタのチャネル形成領域は、酸化物半導体を有し、前記容量素子の容量は、前記液晶素子の容量よりも小さい。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極や走査線(ゲート線)及びデータ線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供する。

【解決手段】半導体膜107と基板との間に第1の絶縁膜を介して設けられた第1の配線102を、半導体膜107と重ねて設け、遮光膜として用いる。さらに半導体膜上にゲート絶縁膜として用いる第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極と第2の配線134を形成する。第1及び第2の配線は、第1及び第2の絶縁膜を介して交差する。第2の配線134の上層には、層間絶縁膜として第3の絶縁膜を形成し、その上に画素電極147を形成する。画素電極147は、第1の配線及び第2の配線とオーバーラップさせて形成することが可能であり、反射型の表示装置において画素電極147の面積を大型化できる。

(もっと読む)

液晶表示装置

【課題】画質の低下を防ぎつつ、消費電力の低減を実現することができる、液晶表示装置

の駆動方法を提案する。

【解決手段】液晶素子と、当該液晶素子への画像信号の供給を制御するトランジスタとを

画素に有する。上記トランジスタは、チャネル形成領域に、シリコン半導体よりもバンド

ギャップが広く、真性キャリア密度がシリコンよりも低い半導体を含み、オフ電流の極め

て小さい。そして、画素を反転駆動させる際に、画素電極を間に挟んで配置されている一

対の信号線に、互いに逆の極性を有する画像信号を入力する。上記構成により、液晶素子

に容量素子を接続しなくても、表示される画質が低下するのを防ぐ。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

薄膜形成基板、薄膜形成方法、及び表示装置の製造方法

【課題】基板に生じるクラックの発生を防止した薄膜形成方法を提供する。

【解決手段】薄膜形成方法は、基板を準備する基板準備工程と、基板上に第1薄膜を形成する第1薄膜形成工程と、第1薄膜に対して光線を相対走査して照射することにより、第1薄膜を結晶化する結晶化工程と、結晶化工程において第1薄膜に生じる熱の基板への伝導量を低下させる緩和層を、結晶化工程の前に、基板の端部領域及び基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

有機薄膜トランジスタ絶縁層材料

【課題】閾値電圧の絶対値及びヒステリシスが小さい有機薄膜トランジスタを製造しうる有機薄膜トランジスタ絶縁層材料を提供すること。

【解決手段】環状エーテル構造を有する繰り返し単位と、酸により脱離しうる有機基を有する繰り返し単位とを含有する高分子化合物(A)を含む有機薄膜トランジスタ絶縁層材料。

(もっと読む)

SOI基板の作製方法および作製装置

【課題】単結晶半導体基板とベース基板の界面に空気層が残ることに起因した、ベース基板から単結晶半導体基板を引き剥がした際に生じる転載不良領域の発生が抑制された、高品位なSOI基板の作製方法および作製に用いる貼り合わせ装置を提供することを課題とする。

【解決手段】ボンド基板を、ベース基板の設置面に対して傾斜角を持たせた状態で貼り合わせる。これにより、貼り合わせ開始箇所を限定できる。また、ボンド基板の一部が支持台からはみ出し、且つ、支持台からはみ出した部分がベース基板に最も近くなる状態にボンド基板を設置した。これにより、ボンド基板とベース基板の接触箇所下部には支持台がなく、ボンド基板の一部は支持台の端部を支点として支持台から浮かんだ状態となり、ベース基板に近づいた部分から順次貼り合わせが進むため、ボンド基板とベース基板の界面に空気層残りが生じることなく安定した貼り合わせを行うことができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

71 - 80 / 12,139

[ Back to top ]