国際特許分類[H01L29/80]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | PN接合ゲートまたは他の整流接合ゲートによって生じる電界効果を有するもの (3,053)

国際特許分類[H01L29/80]の下位に属する分類

PN接合ゲートを有するもの (358)

ショットキーゲートを有するもの (2,351)

国際特許分類[H01L29/80]に分類される特許

41 - 50 / 344

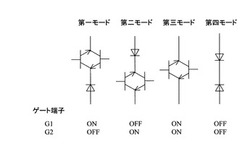

双方向スイッチのゲート駆動方法およびそれを用いた電力変換装置

【課題】インバータ等に適用される半導体デバイスとして双方向デバイスを適用した場合に、意図しない過渡期における各部の過電流や過電圧の発生を未然に防止して、低損失なゲート駆動方法を提供することを目的としている。

【解決手段】第一ゲート端子2、第二ゲート端子3、ドレイン端子4、ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1に適用する駆動方法であり、双方向にオフ状態から双方向にオン状態へと移行する際に、直接移行しないように制御する制御手段を備え、双方向にダイオードを介在させない動作モードで主として動作し、過渡期においてはダイオードを介する動作が可能なため、低損失かつ各部の過電圧、過電流を防止できる効果が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

双方向スイッチのゲート駆動装置

【課題】インバータ等に適用される半導体デバイスとし単方向デバイスを適用した場合に、負荷からの還流電流が流れるタイミングは、還流ダイオードを通して流れるためダイオードにおける損失を取り除けないという課題があった。

【解決手段】第一ゲート端子2、第二ゲート端子3、ドレイン端子4、ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1を使用し、還流電流が流れるタイミングに応じて、第三モードで通電するように前記第一ゲート端子2、および第二ゲート端子3を駆動させる同期制御手段を備えるので、還流ダイオードによる損失を無くすことができ、損失が少なく効率の良いインバータを提供できる双方向スイッチの駆動方法を提供する。

(もっと読む)

双方向スイッチのゲート駆動装置

【課題】インバータ等に適用される半導体デバイスとし単方向デバイスを適用した場合に、負荷からの還流電流が流れるタイミングは、還流ダイオードを通して流れるためダイオードにおける損失を取り除けないという課題があった。

【解決手段】第一ゲート端子2、第二ゲート端子3、ドレイン端子4、ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1を使用し、還流電流が流れるタイミングに応じて、第三モードで通電するように前記第一ゲート端子2、および第二ゲート端子3を駆動させる同期制御手段を備えるので、還流ダイオードによる損失を無くすことができ、損失が少なく効率の良いインバータを提供できる双方向スイッチの駆動方法を提供する。

(もっと読む)

電界効果トランジスタ

【課題】 第1半導体層と第2半導体層とのヘテロ接合により第1半導体層に二次電子ガス層を生じさせつつ、ソース電極とドレイン電極との間の通電状態を切り換えるためのゲート電圧のしきい値を所定の値に調整することができる電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタ10では、サファイア基板11上に、i型のGaNからなるGaN層13と、i型のGaNと格子定数が異なるi型のAlGaNからなるAlGaN層14と、i型のAlGaNよりもエッチングレートが小さいi型のAlInNからなるAlInN層15とが順に形成されている。AlInN層15の上端から途中まで伸びている溝25が形成されており、その溝25の底部の少なくとも一部にゲート電極26がショットキー接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

高電圧耐久III族窒化物半導体デバイス

【課題】高電圧の印加時に、電荷キャリアを導電領域内に抑制して、高電圧耐久性を呈する、HEMTのようなIII族窒化物半導体デバイスを提供する。

【解決手段】高電圧耐久III族窒化物半導体デバイスは、(100)シリコン層14、該(100)シリコン層14上の絶縁体層18、及び該絶縁体層18上のP型導電性の(111)シリコン層16を有する支持基板を備える、高電子移動度トランジスタ(HEMT)を備える。高電圧耐久HEMTは、P型導電性の(111)シリコン層16上に形成したIII族窒化物半導体本体12であって、HEMTのヘテロ接合を形成する、III族窒化物半導体本体も備える。

(もっと読む)

41 - 50 / 344

[ Back to top ]