国際特許分類[H01L29/80]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | PN接合ゲートまたは他の整流接合ゲートによって生じる電界効果を有するもの (3,053)

国際特許分類[H01L29/80]の下位に属する分類

PN接合ゲートを有するもの (358)

ショットキーゲートを有するもの (2,351)

国際特許分類[H01L29/80]に分類される特許

51 - 60 / 344

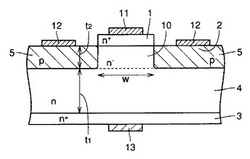

電界効果トランジスタおよびその製造方法

【課題】高耐圧および高電流のスイッチング動作が可能で、かつ製造が容易なFETを提供する。

【解決手段】半導体薄体の一の主表面に設けられた、第1導電型のソース領域(1)と、第1導電型のチャネル領域(10)と、チャネル領域を限定する第2導電型の限定領域(5)と、他の主表面に設けられた第1導電型のドレイン領域(3)と、厚さ方向に連続する第1導電型のドリフト領域(4)とを備え、ドリフト領域(4)およびチャネル領域(10)の不純物濃度は、ソース領域(1)、ドレイン領域(3)および限定領域(5)の不純物濃度よりも低く、チャネル領域(10)の不純物濃度はドリフト領域(4)の不純物濃度よりも低い。

(もっと読む)

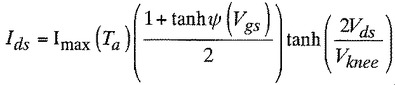

ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータ

【課題】パラメータが物理的な意味をもち、容易に初期値の抽出やデバイス開発へのフィードバックが可能で、電気特性を精度良く表現できるヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータを提供する。

【解決手段】ヘテロ接合電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップST102と、前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップとを備える。

(もっと読む)

電力変換モジュール及びそれを用いた電力変換装置あるいはモータ駆動装置あるいは空気調和機

【課題】インバータ等に適用される半導体デバイスは、寄生ダイオードにより誘導負荷からの還流電流を通流する場合、ダイオードの順方向電圧による損失が大きくなることが懸念され、また双方向デバイスを適用した場合には、2つのゲート端子を駆動する必要があり、制御の複雑化、かつ高コストになるという課題があった。

【解決手段】第一ゲート端子2、第二ゲート端子3、第一ソース端子4、第二ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1に適用する駆動方法であり、第一ゲート端子2あるいは第二ゲート端子3の何れか一方を常時オン状態となるように制御し、還流電流を流す経路を確保しつつ、ダイオード損失を低減し、かつ2つのゲート信号数を減らし、簡易な回路構成、かつ低コストに電源変換回路を実現することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

超伝導体構造、その製造方法、及び電子素子

【課題】鉄砒素系超伝導体の高品質な超伝導薄膜を備えた超伝導体構造、その製造方法、及び電子素子を提供すること。

【解決手段】基板と、前記基板上に形成され、III-V族半導体から成るバッファ層と、前記バッファ層上に形成され、下記式(1)で表される組成を有する超伝導薄膜と、を含み、前記超伝導薄膜におけるAs−As間隔は、前記III-V族半導体におけるV族原子間距離の約1倍であることを特徴とする超伝導体構造。式(1)LnFeAsO1-pFq(式(1)において、Lnは1種以上のランタノイド元素であり、0<p<1、0≦q<1)

(もっと読む)

ヘテロ接合トランジスタ、及びヘテロ接合トランジスタを作製する方法

【課題】チャネル層内の抵抗の不均一を避けることを可能にする構造を有するヘテロ接合トランジスタを提供する。

【解決手段】半導体積層15が、半極性を示すIII族窒化物主面13a上に設けられ、半導体積層15が主面13aに到達する開口16を有する。開口16の側面16aは、III族窒化物半導体のa面に対して大きな角度を成すと共にIII族窒化物半導体のm面に対しても大きな角度を成して、III族窒化物半導体のc面に非常に近い面から構成される。開口16の側面16aの傾斜角は、m面やa面よりもc面に近い。この開口16の側面16aにドリフト層17及びチャネル層19が成長されるので、その成長中に不可避的に取り込まれる不純物量を小さくできる。これ故に、ドリフト層17及びチャネル層19における抵抗の不均一を避けることができる。

(もっと読む)

電子スピン共鳴生成装置および電子スピン共鳴の生成方法

【課題】外部磁場を用いることなく、電子スピン共鳴を生じさせること。

【解決手段】本発明は、半導体からなり、電子の走行方向に対し交差する方向に第1のスピン軌道相互作用に起因した一定の第1有効磁場が生じるチャネル18と、前記チャネル内に前記第1有効磁場に起因して生じた前記電子のスピン分離エネルギに対応する周波数の交流電界を生じさせることにより、前記チャネル内に前記電子の走行方向および前記第1有効磁場の方向に交差する方向に第2スピン軌道相互作用に起因した交流の第2有効磁場を発生させる電極24と、を具備する電子スピン共鳴生成装置である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型化とこれに伴う装置の特性の劣化の抑制とが同時に可能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

51 - 60 / 344

[ Back to top ]