国際特許分類[H01L29/80]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | PN接合ゲートまたは他の整流接合ゲートによって生じる電界効果を有するもの (3,053)

国際特許分類[H01L29/80]の下位に属する分類

PN接合ゲートを有するもの (358)

ショットキーゲートを有するもの (2,351)

国際特許分類[H01L29/80]に分類される特許

71 - 80 / 344

半導体装置及びその製造方法

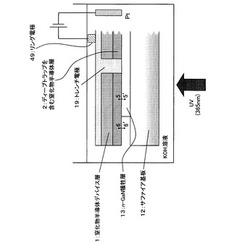

【課題】窒化物半導体デバイス層がエッチングされないようにしながら、窒化物半導体デバイス層を基板から剥離することができるようにする。

【解決手段】半導体装置の製造方法を、基板12上に、エッチング犠牲層13を形成する工程と、エッチング犠牲層13上に、エッチングストッパ層2を形成する工程と、エッチングストッパ層2上に、窒化物半導体デバイス層1を形成する工程と、エッチング犠牲層13を、光電気化学エッチングによって除去する工程とを含むものとし、エッチングストッパ層2を、窒化物半導体デバイス層1に正孔が蓄積することを防止する層とする。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのSBD10は、半導体からなる基板11と、基板11上に形成されたn型層12と、n型層12上に配置されたアノード電極14と、アノード電極14に接続され、n型層12に突出するp型領域13とを備えている。p型領域13は、n型層12との境界領域において、境界領域に隣接するp型領域13内の領域である高不純物領域13Bよりも導電型がp型であるp型不純物の濃度の低い低不純物領域13Aを含んでいる。

(もっと読む)

ヘテロ接合電界効果トランジスタ、その製造方法

【課題】ゲート電極下の電子の走行方向が基板表面に略平行であるようにデバイス構造を改良しながらも各種弊害を解消したヘテロ接合電界効果トランジスタを提供する。

【解決手段】n型導電層は選択的にイオン注入されているシリコン(Si)などのn型不純物をアニール処理で活性化することにより形成されており、n型導電層は、イオンが200keV以上の加速エネルギーで注入されており、p型窒化物半導体層より深く、かつドレイン電極114と導通する半導体層にまで注入イオンが達する選択的イオン注入によって形成されており、n型導電層とn型不純物が注入されていないチャネル領域との接続部115に注入されているn型不純物濃度が1×1018cm−3以下である。

(もっと読む)

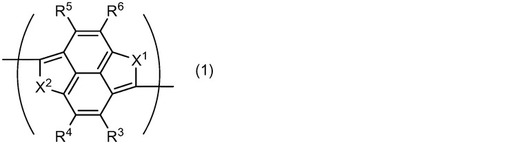

有機薄膜トランジスタ、面状光源及び表示装置

【課題】優れた電界効果移動度を得ることができる有機薄膜トランジスタを提供する。

【解決手段】下式で表される繰り返し単位を有する高分子化合物を含む有機半導体層を備える、有機薄膜トランジスタ。 (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

3−5族化合物半導体

【課題】窒化物系化合物半導体において埋め込み電極として利用可能な特定のパターン形状の導電性材料を埋め込んだ構造を実現し、SIT等のデバイスを作製可能にする。

【解決手段】(1)一般式InxGayAlzN(ただし、x+y+z=1、0≦x≦1、0≦y≦1、0≦z≦1)で表される第1の3−5族化合物半導体と、(2)これに接して該第1の3−5族化合物半導体表面の一部を特定のパターン形状で被覆するSiO2と、(3)該SiO2に接して積層された導電性材料と、(4)該SiO2と該導電性材料との積層体で被覆されてない該第1の3−5族化合物半導体表面の露出部と該導電性材料とを共に被覆する一般式InuGavAlwN(ただし、u+v+w=1、0≦u≦1、0≦v≦1、0≦w≦1)で表される第2の3−5族化合物半導体と、からなり、該導電性材料の層厚が5nm以上100nm以下であることを特徴とする3−5族化合物半導体。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電圧0Vにおけるリーク電流を低減し、十分なノーマリオフ動作を実現可能な縦型チャネル構造の電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明の電界効果トランジスタは、高濃度n型GaN層102と、高濃度n型GaN層102の上に形成され、平坦部124及び凸部122が表面に設けられ、高濃度n型GaN層102のキャリア濃度よりも低いキャリア濃度を有するn型GaN層103と、凸部122の上面に形成されたWSiソース電極105と、高濃度n型GaN層102と電気的に接続されたTi/Alドレイン電極109と、凸部122の側面に接するように平坦部124の上に形成されたp型ZnO層106と、p型ZnO層106の上に形成されたNi/Auゲート電極107とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法、半導体基板の判定方法、および電子デバイス

【課題】電圧対電流特性の線形性が改善された高性能の化合物半導体エピタキシャル基板、その製造方法およびその判定方法を提供する。

【解決手段】2次元キャリアガスを生成する化合物半導体114と、当該化合物半導体114にキャリアを供給するキャリア供給半導体120と、当該化合物半導体114と当該キャリア供給半導体120との間に配置され、キャリアの移動度を当該化合物半導体におけるキャリアの移動度よりも小さくする移動度低減因子を有する移動度低減半導体116とを備える半導体基板。

(もっと読む)

3−5族化合物半導体

【課題】窒化物系化合物半導体において埋め込み電極として利用可能な特定のパターン形状の導電性材料を埋め込んだ構造を実現し、SIT等のデバイスを作製可能にする。

【解決手段】(1)GaN層上にGaAlNを積層した構造である第1の3−5族化合物半導体と、(2)これに接して該第1の3−5族化合物半導体表面の一部を特定のパターン形状で被覆する導電性材料と、(3)該導電性材料で被覆されてない該第1の3−5族化合物半導体表面の露出部と該導電性材料とを共に被覆する一般式InuGavAlwN(ただし、u+v+w=1、0≦u≦1、0≦v≦1、0≦w≦1)で表される第2の3−5族化合物半導体と、からなり、該導電性材料の層厚が5nm以上100nm以下である3−5族化合物半導体。

(もっと読む)

トランジスタ

【課題】ノーマリーオフ型であるとともに、ゲート閾値電圧のばらつきが小さいHEMT型のトランジスタを提供する。

【解決手段】このトランジスタは、p型領域18と、チャネル領域20と、バリア領域22と、絶縁膜62と、ゲート電極64を備えている。チャネル領域20は、n型またはi型であり、p型領域の表面に接しており、第1チャネル領域と第2チャネル領域を有している。バリア領域22は、第1チャネル領域の表面とヘテロ接合している。絶縁膜62は、第2チャネル領域の表面、及び、バリア領域の表面に接している。ゲート電極64は、絶縁膜62を介して第2チャネル領域及びバリア領域に対向している。第1チャネル領域と第2チャネル領域は、電流経路において直列に配置されている。

(もっと読む)

71 - 80 / 344

[ Back to top ]