国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

201 - 210 / 1,392

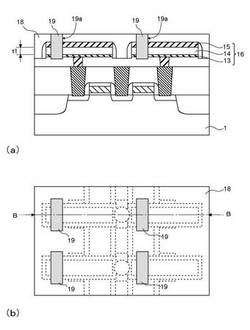

半導体記憶装置及び半導体記憶装置の製造方法

【課題】相変化材料を記録層とするエッジコンタクト型メモリセルにおいて、被覆率の悪化による記録層の膜厚ばらつきによる下部電極と上部電極間の距離が変動し、この変動に基づきキャパシタ特性がばらつく(抵抗値の変動)ことを抑制する。

【解決手段】下部電極13、電極間絶縁膜14、上部電極15からなる積層膜16を形成し、この積層膜の各層側面を露出する凹部19aに相変化材料を埋設して記録層19とすることで記憶素子を構成すると、下部電極13と上部電極15間の距離は電極間絶縁膜14の厚みt1で一定となり、特性ばらつきを抑制することができる。

(もっと読む)

情報記録再生装置

【課題】高記録密度及び低消費電力の情報記録再生装置を提案する。

【解決手段】実施形態に係わる情報記録再生装置は、記録層12と、記録層12に電圧を印加して記録層12に相変化を発生させて情報を記録する記録回路とを備える。記録層12は、少なくとも1種類の陽イオン元素と少なくとも1種類の陰イオン元素を有する化合物から構成され、陽イオン元素の少なくとも1種類は、電子が不完全に満たされたd軌道を有する遷移元素であり、隣接する陽イオン元素間の平均最短距離は、0.32nm以下である。記録層12は、(i) AxMyX4 (0≦x≦2.2、1.8≦y≦3)、(ii) AxMyX3 (0≦x≦1.1、0.9≦y≦3)及び(iii) AxMyX4 (0≦x≦1.1、0.9≦y≦3)のうちから選択される材料を備える。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

記憶装置

【課題】精確に記憶素子の状態を判別できる記憶装置を提供する。

【解決手段】メモリセル11を複数備えたメモリアレイ10と、読み出し対象のメモリセル11の状態を判別する読み出し回路20を設ける。メモリセル11は抵抗変化素子13を含み、読み出し回路20に備えられた参照メモリセル22は抵抗変化素子23を含む。抵抗変化素子23および抵抗変化素子13は同一の構成材料からなり、抵抗変化素子23の面積は、抵抗変化素子13の面積よりも大きい。読み出し電圧の大きさに対する抵抗変化素子23の抵抗値の変化は、抵抗変化素子13の抵抗値の変化と対応する。

(もっと読む)

記憶素子および記憶装置

【課題】良好なデータ保持特性を維持しつつ、安定したスイッチング特性を有する記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20はイオン源層21と、抵抗変化層22と、抵抗変化層22よりも高い導電率を示すバリア層23とを有する。これにより、データ消去時における電流パスあるいは不純物準位を形成する金属イオンの移動効率が改善される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 可変抵抗膜を有する半導体装置の電気的特性のバラツキを低減する。

【解決手段】 半導体装置の製造方法は、導電性材料を含み、所定方向に沿って延在する柱状体を形成する工程と、形成された柱状体の所定方向の一部を酸化させ、所定方向に見て、導電性材料の酸化物からなる可変抵抗部が未酸化の導電性材料に挟まれた構造を一体的に形成する工程と、を含む

(もっと読む)

半導体装置およびその製造方法

【課題】高品質な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、第1の配線L2(i)と、第1の配線と交差する第2の配線L3(j)と、第1の配線と第2の配線とが交差する各領域に設けられ、一端が第1の配線に接続され、且つ他端が第2の配線に接続され、可変抵抗素子25及び非オーミック素子D−mimが直列接続されたメモリセル構造CUsと、を備え、非オーミック素子は、絶縁層22として、第1の層22aと、第1の層のバンドギャップとは異なるバンドギャップを有し、第1の層上に設けられた第2の層22bと、第2の層のバンドギャップとは異なるバンドギャップを有し、第2の層上に設けられた第3の層22cとを備えている。

(もっと読む)

記憶装置及びその製造方法

【課題】信頼性が高い記憶装置及びその製造方法を提供する。

【解決手段】記憶装置1は、複数の微小導電体が隙間32を介して集合したナノマテリアル集合層23と、隙間32内に配置された絶縁材料25と、を備える。微小導電体はカーボンナノチューブ31であり、カーボンナノチューブ31が延びる方向は、ナノマテリアル集合層23の下面に対して垂直な方向よりも、下面に対して平行な方向に近く、ナノマテリアル集合層23の下面に接した下部電極層22と、ナノマテリアル集合層23の上面に接した上部電極層24と、をさらに備え、下部電極層22及び上部電極層24の双方に接した微小導電体が存在しない。

(もっと読む)

記憶装置

【課題】高密度化および大容量化が可能な記憶装置を提供する。

【解決手段】基板11上に複数の平行なワード線WLと複数の平行な第1ビット線1BLとが互いに垂直な方向に設けられている。隣接する2本のワード線WLの間に、ビットコンタクト電極BCが設けられている。ビットコンタクト電極BCを挟んで隣接する2本のワード線WLのそれぞれを間にしてビットコンタクト電極BCと反対側に、ノードコンタクト電極NCが設けられている。ノードコンタクト電極NCは、接続層23を介して下部電極21に接続されている。下部電極21は、基板11の表面に平行な面内においてノードコンタクト電極NCの直上からビットコンタクト電極BCに近づく方向にずれた位置に設けられている。複数の第2ビット線2BLの各々は、第1ビット線1BLの両側のノードコンタクト電極NCに接続された下部電極21に重なっている。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】カーボンナノチューブを可変抵抗素子として用い消費電力の抑制とスイッチの誤作動の低減を両立した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置の製造方法は、半導体基板9上に、下部電極を形成する工程と、前記下部電極の上にカーボンナノチューブを含む可変抵抗層11を形成する工程と、前記可変抵抗層に電子線或いは光子線を照射する照射工程と、前記照射工程の後に、前記可変抵抗層の上に上部電極を形成する工程とを含む。

(もっと読む)

201 - 210 / 1,392

[ Back to top ]