国際特許分類[H02M1/08]の内容

電気 (1,674,590) | 電力の発電,変換,配電 (135,566) | 交流−交流,交流−直流または直流−直流変換装置,および主要な,または類似の電力供給システムと共に使用するための装置:直流または交流入力−サージ出力変換;そのための制御または調整 (22,926) | 変換装置の細部[1,2007.01] (2,099) | 静止型変換器に用いられる半導体装置の制御電圧の発生に用いられる回路 (988)

国際特許分類[H02M1/08]の下位に属する分類

多相システムのいくつかの相に共通な制御回路に使用するもの

直列または並列接続された半導体装置の同時制御のためのもの (7)

国際特許分類[H02M1/08]に分類される特許

51 - 60 / 981

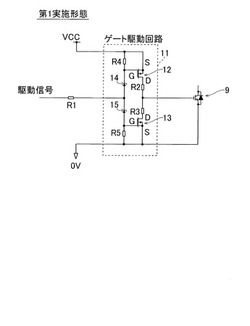

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

電源装置の駆動回路及び電源装置

【課題】遷移期間においてハイサイドトランジスタQ1がオンしないようにする。

【解決手段】高電位電源ラインと低電位電源ラインとの間に直列に接続されたハイサイドトランジスタとロウサイドトランジスタと,両トランジスタの接続ノードと出力端子との間に設けられたインダクタとを有する電源装置の前記両トランジスタを駆動する駆動回路であって,前記ハイサイドトランジスタのゲートを駆動する第1のゲートドライバと,前記ロウサイドトランジスタのゲートを駆動する第2のゲートドライバとを有し,前記ハイサイドトランジスタがオンでロウサイドトランジスタがオフの第1の状態から,前記ハイサイドトランジスタがオフでロウサイドトランジスタがオンの第2の状態に遷移する遷移期間で,前記第1のゲートドライバは前記ハイサイドトランジスタのゲートを前記低電位電源ラインの電位より低い第1の電圧に駆動する電源装置の駆動回路。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

電力変換装置

【課題】還流ダイオードの逆回復による損失を低減し、スイッチング時に発生する振動を抑制する電力変換装置を提供することにある。

【解決手段】電力変換装置1は、対になる2つのスイッチング素子4a,4bと、スイッチング素子4a,4bのそれぞれに逆並列に接続された還流ダイオード5a,5bと、スイッチング素子4a,4bに印加される主電圧よりも低い電圧の補助電源21a,21bと、スイッチング素子4aのターンオフ後からスイッチング素子4bのターンオンまでの間に、スイッチング素子4a及び還流ダイオード5aに補助電源21aの電圧を印加し、スイッチング素子4aのターンオン動作中に、スイッチング素子4aのスイッチング速度を変化させる主素子制御回路6aとを備える。

(もっと読む)

電源回路

【課題】主スイッチング素子の面積を大きくすることなく、ゲートの容量に蓄積された電荷を引き抜く引き抜き期間を短くすることができる電源回路を提供する。

【解決手段】Nチャネル型の主スイッチング素子10と、主スイッチング素子10を制御する駆動回路30と、主スイッチング素子10の第2電極端子に接続される負バイアス回路20とを備える。そして、負バイアス回路20を、接地された第1抵抗21と、当該第1抵抗21と第2電極端子との間に配置されて第2電極端子との接続点の電位を第1抵抗21との接続点の電位より低くする電位降下手段22、23とを有するものとする。また、駆動回路30を第1抵抗21と電位降下手段22、23との接続点に接続する。そして、主スイッチング素子10がオフされたとき、ゲートの容量に蓄積された電荷を駆動回路30および第1抵抗21と電位降下手段22、23との接続点を介して引き抜くようにする。

(もっと読む)

ゲート駆動装置

【課題】動作条件が変化しても、損失およびノイズ特性に優れたスイッチング制御を実現できるゲート駆動装置を得ることを目的としている。

【解決手段】定電流駆動回路11Cと、定電圧駆動回路11Vと、スイッチング素子2の動作条件をパラメータとして、定電流駆動回路11Cおよび定電圧駆動回路11Vのそれぞれでスイッチング素子2を駆動させたときの、スイッチング損失および放射ノイズの一方または両方についての情報を保持する回路特性情報保持部15と、スイッチング素子2の動作条件を検出する動作条件検出部14と、検出した動作条件と、保持する回路特性情報に基づき、定電流駆動回路11Cと定電圧駆動回路11Vのうちのいずれか一方をスイッチング素子2の駆動回路として切替える駆動回路切替部12、13とを備えるように構成した。

(もっと読む)

ドライバーIC入力段の放電経路回路

【課題】ヘッドランプの動きを精密に制御することができるドライバーICの電源部に用いられる放電経路回路を提供する。

【解決手段】第1入力に連結される電源入力ポート及び第2入力に連結される動作モード選択ポートを備えた集積回路ICの入力段の放電経路を提供する回路であって、前記電源入力ポートと前記第1入力との間に連結されて、電源上のノイズをフィルタリングするLCフィルタと、前記第1入力と接地との間に連結される抵抗素子と、を含み、前記抵抗素子は、前記LCフィルタにより充電された電圧を放電するための放電経路を提供する。

(もっと読む)

スイッチング回路及びDC−DCコンバータ

【課題】スイッチ素子の破壊を防止したスイッチング回路及びDC−DCコンバータを提供する。

【解決手段】ハイサイドスイッチと、整流要素と、駆動回路と、を備えたスイッチング回路が提供される。前記ハイサイドスイッチは、高電位端子と出力端子との間に接続されている。前記整流要素は、前記出力端子と低電位端子との間に、前記低電位端子から前記出力端子に向かう方向を順方向として接続される。前記駆動回路は、入力されるハイサイド制御信号に応じて前記ハイサイドスイッチの制御端子に第1の電圧を供給してオンさせ、前記出力端子の電圧が規定値以上に上昇したとき前記ハイサイドスイッチの制御端子に前記第1の電圧よりも高い第2の電圧を供給する。

(もっと読む)

ゲート駆動装置

【課題】ゲート駆動装置で駆動される複数個のスイッチングデバイスにおけるVth、ミラー電圧のバラツキによるスイッチング速度のバラツキを抑え、かつ損失のバラツキを最小限とすることができるゲート駆動装置を得ることを目的とする。

【解決手段】スイッチングデバイス1へのゲート信号を定電流出力で作成する定電流パルスゲート駆動回路2、ゲート信号を定電圧出力で作成する定電圧パルスゲート駆動回路3、および定電流パルスゲート駆動回路2の動作と定電圧パルスゲート駆動回路3の動作との切替を行う判定/切替回路4を備えた。

(もっと読む)

電力変換装置用の駆動回路および電力変換装置

【課題】上側のスイッチング素子の誤動作を抑制できる電力変換装置用の駆動回路を提供する。

【解決手段】第1回路10は、直流電源E1の低電位端と高電位端との間で相互に直列に接続される第1素子11及び第2素子12を有し、第1素子11は高電位端側に設けられ、第2素子12は低電位端側に設けられる。第1素子11及び第2素子12は、その両方がスイッチである。第2回路20は、第2素子12の両端の電圧が所定値よりも大きいときにスイッチング素子Tx1を非導通とし、当該電圧が所定値よりも小さいときにスイッチング素子Tx1を導通させる。スイッチ素子32は、第1素子11と並列に接続され、スイッチング素子Tx1が非導通である状態で導通し、スイッチング素子Tx1が導通する状態で非導通する。

(もっと読む)

51 - 60 / 981

[ Back to top ]