国際特許分類[H02M1/08]の内容

電気 (1,674,590) | 電力の発電,変換,配電 (135,566) | 交流−交流,交流−直流または直流−直流変換装置,および主要な,または類似の電力供給システムと共に使用するための装置:直流または交流入力−サージ出力変換;そのための制御または調整 (22,926) | 変換装置の細部[1,2007.01] (2,099) | 静止型変換器に用いられる半導体装置の制御電圧の発生に用いられる回路 (988)

国際特許分類[H02M1/08]の下位に属する分類

多相システムのいくつかの相に共通な制御回路に使用するもの

直列または並列接続された半導体装置の同時制御のためのもの (7)

国際特許分類[H02M1/08]に分類される特許

41 - 50 / 981

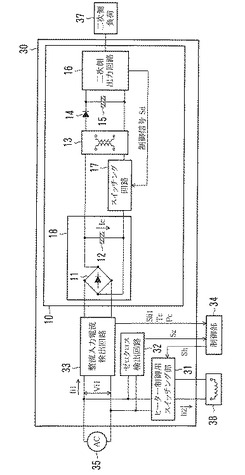

電力制御方法、電力制御装置および画像形成装置

【課題】コンデンサインプット形の整流回路を用いているにもかかわらず、入力電流のピーク値を抑えることのできる電力制御を低コストで実現すること。

【解決手段】交流電源35からの交流電力をコンデンサインプット形のレギュレーター10により整流して二次側負荷に供給し、かつ、交流電源35からの交流電力をヒーター38に供給するための電力制御方法である。この電力制御方法は、ヒーター38に流れ込むヒーター入力電流Ii2を各半サイクルの全期間においてオンとする第1モード、および、ヒーター入力電流Ii2の各半サイクルにおいて、レギュレーター10においてコンデンサの充電電流Icに起因する入力充電電流Ii3が流れている期間はヒーター入力電流Ii2をオフとしそれ以外の期間はヒーター入力電流Ii2をオンとする第2モード、が設けられ、第1モードまたは第2モードを選択して用いることにより制御を行う。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

パワー半導体モジュール

【課題】 電力損失が小さく、発生ノイズが小さいパワー半導体モジュールを実現する。

【解決手段】 ワイドバンドギャップ半導体を利用したユニポーラ型スイッチング素子(ワイドバンドギャップ半導体スイッチング素子)1とシリコン半導体を利用した絶縁ゲート型バイポーラトランジスタ(Si−IGBT)2を並列接続したパワー半導体モジュールで、ワイドバンドギャップ半導体素子1のチップ面積はSi−IGBT2のチップ面積よりも小さいことを特徴とする。

(もっと読む)

ゲート駆動回路

【課題】ターンオン時のスイッチング特性が変動せず、また、電流回生時の電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲート駆動回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるノーマリオフ型スイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲート駆動回路であって、制御回路とスイッチング素子のゲートとの間に接続され、コンデンサC1と抵抗R1との直列回路と並列にノーマリオン型スイッチグ素子Q2が接続され、スイッチング素子Q2のゲートはGNDに接続され、スイッチング素子Q1のゲート電圧に応じたゲートバイアス電流を供給し、スイッチング素子Q1のオフ時にはゲート・ソース間を短絡する。

(もっと読む)

負荷回路の制御装置

【課題】並列に接続したMOSFETの発熱を均一化することが可能な負荷回路の制御装置を提供する。

【解決手段】電源と負荷とを接続する負荷回路に、2個のMOSFET(Q1),(Q2)を並列に配置する。そして、各MOSFET(Q1),(Q2)が交互にオン、オフとなるように制御する。その結果、各MOSFET(Q1),(Q2)のいずれか一方にのみ電流が流れることになるので、電流センサ12,22で検出されるオフセット誤差は、いずれか一方のオフセット誤差のみとなり、高精度な電流検出が可能となる。従って、負荷に流れる電流が過電流となった際に回路を遮断する制御を行う際に、高精度な遮断制御が可能となる。

(もっと読む)

ブートストラップ回路、半導体装置

【課題】ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供する。

【解決手段】ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。

(もっと読む)

電力変換装置

【課題】スイッチング素子を複数並列に接続して逆変換器等を構成した場合にも簡易かつ確実に電流アンバランスを解消することができる電力変換装置を提供する。

【解決手段】ゲート調整回路12は、基準素子ユニット501における直流電流検出器541の直流電流の検出値Id1および、基準素子ユニット501以外の素子ユニット502における直流電流検出器542の直流電流の検出値Id2に基づいて、それぞれ時間γ1および時間γ2から時間差Δtを電流アンバランス量として算出する。ゲート調整回路12は、時間差Δtを次の第1状態におけるターンオフのタイミングで、ゲート駆動回路552uの動作信号S2uに遅延時間として付加する。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

ゲート駆動回路

【課題】ワイドギャップ半導体のターンオフの速度を高速化できるゲート駆動回路。

【解決手段】負極が接地された正電源E1と、正極が接地された負電源E2と、正電源の正極と負電源の負極との間に設けられ、制御信号を生成する制御回路11と、正電源の正極と負電源の負極との間に設けられたトランジスタQ1とトランジスタQ2との直列回路と、ドレイン端子、接地されたソース端子及びQ1とQ2との接続点に接続されたゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子GaNFETと、制御信号のオフ時にQ1を所定時間だけオンさせQ1を介して負電源の電圧をスイッチング素子のゲート端子に印加するターンオフ制御回路13と、スイッチング素子のゲート端子と接地との間に設けられ、制御信号のオフ時にそのゲート端子とソース端子を短絡させるトランジスタQ3とトランジスタQ4との直列回路を備える。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

41 - 50 / 981

[ Back to top ]