国際特許分類[H03B5/20]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が抵抗とキャパシタンスまたはインダクタンスのいずれか一方とからなるもの,例.位相発振器 (38)

国際特許分類[H03B5/20]の下位に属する分類

増幅器の能動素子が真空管であるもの

増幅器の能動素子が半導体装置であるもの (1)

周波数決定素子が,信号が伝送される閉リング中のブリッジ回路の一部であるもの;周波数決定素子がブリッジ回路を経て,上記閉リングに結合されているもの,例.ウイーンブリッジ発振器,並列T型発振器 (4)

国際特許分類[H03B5/20]に分類される特許

11 - 20 / 33

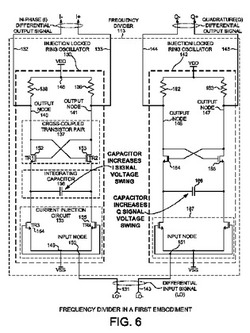

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

MOSFETのソースバルク電圧を用いた信号処理ASIC用の温度補償RC発振器

温度補償CMOS RC発振回路は、抵抗と温度相関バイアス電流とを用いてソースバルク電圧を変化させて、温度に対するMOSFETの閾値電圧の変動を安定させる。この温度層間バイアス電流はまた、抵抗を流れる。温度が上昇すると、バイアス電流も増え、MOSFETのソースバルク電圧を上昇させる。上昇したソースバルク電圧は、高い温度にてMOSFETの閾値電圧を安定させるのを補助する。この発振器には省電力ロジックも組み込まれており、低い電力消費で高い周波数が得られる。本発明では、得られる発振器が低出力設計となってしまう高利得オペアンプや高速比較器はなく、他のシステムとともにシングルチップに組み込むことができる。 (もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

温特補正機能付き発振回路およびその製造方法

【課題】 発振周波数を補正するためのメモリなどが不要な温特補正機能付き発振回路およびその製造方法を実現する。

【解決手段】 温特補正機能付き発振回路10は、第1の発振回路21と、第2の発振回路22と、第1の発振回路21が発生する発振周波数を理想の発振周波数に近い発振周波数に補正するための補正回路50とを備える。補正回路50は、第1の発振回路21の発振周波数f1と、第2の発振回路22の発振周波数f2との差分(f1−f2)を検出し、その検出した差分に補正係数αを乗じ(α・(f1−f2))、その補正された差分を第1の発振回路21の発振周波数に加算し(f1+α・(f1−f2))、それを出力する動作を行う。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、第1電圧供給回路13、第2電圧供給回路14及び調整値生成回路16を備えている。第1電圧供給回路13は、基準時間で第1電圧V1が基準電圧Vrefに到達するような時定数となる抵抗値の抵抗器R1とキャパシタン

スのキャパシタC1とを備える。第2電圧供給回路14は、発振回路11の周波数に応じたパルス信号S1,S2によってスイッチングを行なう第1及び第2スイッチング手段SW1,SW2によって第2電圧V2を上昇させる。調整値生成回路16は、第2電圧V2が第1電圧V1よりも先に基準電圧Vrefになった場合には、周波数を低くする調整値を

発振回路11に供給し、第2電圧V2が第1電圧V1よりも遅れて基準電圧Vrefになっ

た場合には、周波数を高くする調整値を発振回路11に供給する。

(もっと読む)

発振回路

【課題】従来の発振回路は、発振信号を増幅させる電流等の影響で発振周波数の高速化が制限されるという問題があった。

【解決手段】本発明にかかる差動発振回路は、帰還ループ回路を備えた差動型の発振回路であって、帰還ループ回路上に縦続接続され、入力された一対の差動入力信号を遅延させて一対の差動出力信号として出力する遅延回路2〜5と、発振回路が発振起動状態か安定状態のいずれかにあるかを検出し、検出結果を示す検出信号VSTPを出力する発振起動検出回路7と、を備える。さらに遅延回路2〜5は、発振起動検出回路7から出力された検出信号VSTPに基づいて、差動出力信号の出力電流値を制御する。このような回路構成により、発振周波数の高速化が可能である。

(もっと読む)

発振回路、集積回路装置及び電子機器

【課題】複数の周波数のうちから所望の周波数を選択してクロック信号を生成できる発振回路、集積回路装置及び電子機器を提供すること。

【解決手段】発振回路は、キャパシター10の一端、第1の抵抗素子20の一端及び第2の抵抗素子30の一端がその入力に接続される第1の反転回路と、キャパシター10の他端がその出力に接続される第n(nは2以上の偶数)の反転回路とを有する第1〜第nの反転回路INV1〜INVnと、第nの反転回路INVnの出力が入力され、第1の抵抗素子20の他端を駆動する第1の駆動用反転回路DR1と、第nの反転回路INVnの出力が入力され、第2の抵抗素子30の他端を駆動する第2の駆動用反転回路DR2とを含む。

(もっと読む)

発振回路

【課題】振動子の安定発振を早める発振回路に関する技術を提供するとともに、それを用いた超音波流量計を提供する。

【解決手段】共振周波数を有する振動子1と、前記振動子に接続されるアンプ2と、付勢パルス発生手段3と、前記付勢パルス発生手段3と前記振動子1およびアンプ2との接続・非接続とを切替える切替え手段4とを備え、前記振動子1の駆動初期は前記切替え手段4により、前記振動子1と前記付勢パルス発生手段3とを接続するようにした発振回路。

(もっと読む)

CR発振クロック内蔵マイクロコンピュータ

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

集積回路

【課題】CR発振回路を構成するコンデンサの充放電切換りタイミングと、論理回路を構成するCMOSインバータに貫通電流が流れるタイミングとをずらすことで、周波数が安定した発振信号を発生する集積回路を提供する。

【解決手段】複数のCMOS素子によって構成された論理回路と、論理回路に、容量素子と抵抗素子の時定数に依存する周波数の発振信号を出力するCR発振回路と、論理回路に入力される発振信号を遅延する遅延回路と、を備え、CR発振回路と電源とを接続する電源配線が、論理回路と電源とを接続する電源配線と接続されている。

(もっと読む)

11 - 20 / 33

[ Back to top ]