国際特許分類[H03F3/50]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 増幅素子の入出力回路に共通なインピーダンスに入力を加えまたはそれから出力を取り出す増幅器,例.カソードホロワ (35)

国際特許分類[H03F3/50]の下位に属する分類

電子管のみをもつもの

国際特許分類[H03F3/50]に分類される特許

1 - 10 / 35

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

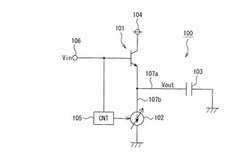

ダブルソースフォロア回路

【課題】電流源によって流れる電流量を増大させることなく、出力信号の立ち上り、立ち下りを高速化することができるダブルソースフォロア回路を提供する。

【解決手段】nMOSFET102を含むソースフォロア回路と、nMOSFET102とは極性が異なるpMOSFET101を含むソースフォロア回路と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路に入力信号を入力する入力端子111と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路から出力信号を出力する共通の出力端子112)と、を含むダブルソースフォロア回路を構成する。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】オフセット補償機能付き駆動回路190は、入力電位に応じたレベルの出力電位を出力するプッシュ型駆動回路160と、駆動回路160のオフセット電圧VOFを補償するオフセット補償回路とを備える。オフセット補償回路は、キャパシタ122およびスイッチS1〜S4を含む。スイッチS1,S2をオンしてキャパシタ122をオフセット電圧VOFに充電し、次にスイッチS3をオンしてVI+VOFを駆動回路160に与え、次いでスイッチS4をオンしてVO=VIとする。したがって、消費電流を低減し、オフセット電圧VOFを補償できる。

(もっと読む)

ソースフォロア回路

【課題】複数段構成におけるソースフォロア回路において入出力レンジを確保する。

【解決手段】ソースフォロア部SF11、SF12間に、ゲートドレイン間がダイオード接続され且つソースフォロア部SF11およびSF12を構成するMOSトランジスタM11およびM12と同一チャネル種類のMOSトランジスタM13とそのドレインに接続された電流源C13とからなる接続部11を設け、前段のソースフォロア部SF11の出力端とMOSトランジスタM13のソースとを接続し、MOSトランジスタM13のドレインと後段のソースフォロア部SF12の入力端とを接続する。接続部11における入出力間の電圧レベルのシフト方向は、ソースフォロア部SF11、SF12における入出力間の電圧レベルのシフト方向と逆となり、電圧シフトを打ち消す方向に作用するため、電圧レベルのシフトにより入出力レンジが狭くなることを抑制することが可能となる。

(もっと読む)

ソースフォロア回路

【課題】消費電力の増加を抑制しつつ、負荷回路からのキックバックを抑制する。

【解決手段】MOSトランジスタM11と、ゲートおよびドレイン間がダイオード接続されたMOSトランジスタM12と、電流源C11とを直列接続してソースフォロア回路10を構成する。MOSトランジスタM11のゲートに入力された、ソースフォロア回路10への入力信号Vinは、MOSトランジスタM11によりほぼ1倍の利得で出力され、さらに、ダイオード接続されたMOSトランジスタM12でほぼ1倍の利得で出力され、これがソースフォロア回路10の出力信号Voutとして出力されるため、結果的に、1段構成のソースフォロア回路と同様の動作をするが、その消費電力は少なくてすむ。

(もっと読む)

高速入力インターフェース回路

【課題】高周波における入力インピーダンス整合が改善された、広帯域な高速入力インターフェース回路を提供する。

【解決手段】抵抗R1は、その一端が入力端子DTに接続され、他端がインダクタL1を介して第1の電源端子VCCに接続されている。また、抵抗R2は、その一端が入力端子DCに接続され、他端がインダクタL2を介して電源端子VCCに接続されている。また、抵抗R3は、その一端が入力端子DTに接続され、他端がインダクタL3を介して第2の電源端子VEEに接続されている。また、抵抗R4は、その一端が入力端子DCに接続され、他端がインダクタL4を介して電源端子VEEに接続されている。

(もっと読む)

ソースフォロア回路

【課題】電流源側の駆動能力の大幅な改善を図り、回路の消費電力やエリアの大幅な削減を図るようにしたソースフォロア回路の提供。

【解決手段】この発明は、入力電圧を受けるMOSトランジスタM1と、MOSトランジスタM1とカスコード接続される電流源10とを備えている。電流源10は、MOSトランジスタM1とカスコード接続されるMOSトランジスタM2と、MOSトランジスタM1とMOSトランジスタM2との共通接続部と、MOSトランジスタM2のゲートとの間に接続されるコンデンサC1と、MOSトランジスタM2のバイアスを印加する経路上に配置される抵抗R1とを備えている。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶

縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、

しきい値電圧や移動度にバラツキが生じる。

【解決手段】本発明は、容量素子の両電極がある特定のトランジスタのゲート

・ソース間電圧を保持できるように配置した電気回路を提供する。そして本発明

は、容量素子の両電極間の電位差を定電流源を用いて設定できる機能を有する電

気回路を提供する。

(もっと読む)

1 - 10 / 35

[ Back to top ]