国際特許分類[H03F3/60]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 結合回路網が分布定数をもつ増幅器,例.導波管共振器をもつもの (397)

国際特許分類[H03F3/60]に分類される特許

21 - 30 / 397

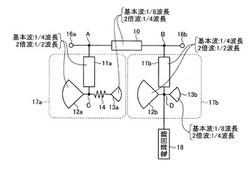

高調波抑圧回路

【課題】高周波動作と、低コスト化および小型化とを両立させることが可能な高調波抑圧回路を得ること。

【解決手段】基本波の1/8波長の長さを有し、一端が入力端16aを形成し、他端が出力端16bを形成する主線路10と、一端が主線路10の入力端16aに接続された基本波の1/4波長の長さを有する第1の線路11aと、第1の線路11aの他端に一端が接続された抵抗体14および基本波の1/4波長の長さを有する第1のオープンスタブ12aと、抵抗体14の他端に接続された基本波の1/8波長の長さを有する第2のオープンスタブ13aと、一端が主線路10の出力端16bに接続された基本波の1/4波長の長さを有する第2の線路11bと、第2の線路11bの他端に接続された基本波の1/4波長の長さを有する第3のオープンスタブ12bおよび基本波の1/8波長の長さを有する第4のオープンスタブ13bと、を備える。

(もっと読む)

リニアライザ

【課題】ダイオードから見るインピーダンスが変化しても、利得特性と位相特性の単調変化を実現することができるリニアライザを得ることを目的とする。

【解決手段】アノードが信号路3に接続されて、順方向に電圧が印加されているダイオード15と、アノードが信号路4に接続されて、順方向に電圧が印加されているダイオード16とを備え、ダイオード15のカソードとダイオード16のカソードとの接続点がバイアス接地用ビアホール17に接地されている。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

広帯域マイクロ波増幅器

【課題】クラスEのHPAが広い帯域幅にわたって同時に高いPAE及び電力を維持することを可能にする。

【解決手段】スイッチングモード電力増幅器の出力に結合されたシャント誘導素子と、前記増幅器の前記出力に結合されている直列の誘導素子と、前記直列の誘導素子に結合されている直列の容量素子とを含む構成とした。

(もっと読む)

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

分布定数型増幅器

【課題】分布定数型差動増幅器の出力波形におけるジッタを低減する。

【解決手段】分布定数型増幅器は、複数の増幅器を有する。複数の増幅器はそれぞれ、固有の遅延時間を持って一の信号源からの入力信号を受ける。また、複数の増幅器はそれぞれ、固有の遅延時間に対応する遅延時間をもって共通の負荷に出力信号を提供する。複数の増幅器それぞれに関して、固有の遅延時間と対応する遅延時間の和は等しく設定されている。複数の増幅器のそれぞれは、一対の差動トランジスタと、該一対の差動トランジスタと当該増幅器の出力との間に直列に挿入された一対のカスコードトランジスタを含む。一対の差動トランジスタは、当該一対の差動トランジスタそれぞれのコレクタ−ベース間の接合容量が準飽和領域の接合容量となるように、バイアスされている。

(もっと読む)

光変調器駆動回路

【課題】分布定数型増幅器を用いた光変調器の駆動回路であって、光変調器からの光出力の立ち上がり時間や立ち下がり時間を短くし得る駆動回路を提供する。

【解決手段】光変調器駆動回路は、複数の第1の非反転増幅器及び反転増幅器を備える。第1の非反転増幅器は、入力端と出力端との間に設けられている。第1の非反転増幅器はそれぞれ、入力端からの入力信号を固有の遅延時間で受け、出力端において第1の遅延時間で出力信号を与える。反転増幅器は、入力端と出力端との間に設けられている。反転増幅器は、入力信号を受け、出力端において第1の遅延時間より大きい第2の遅延時間で出力信号を与える。

(もっと読む)

高調波処理回路、高周波増幅器及び高周波発振器

【課題】広帯域での2倍波整合を取れず、高効率化できる周波数範囲が狭い。

【解決手段】伝送線路2から構成されるメイン線路と、抵抗6と伝送線路5、7とが直列接続された回路から構成され、メイン線路と並列接続されたサブ線路と、一端がメイン線路とサブ線路との接続点に接続されたオープンスタブ3、4とを含んで構成される。

(もっと読む)

分配回路、送信用フェーズドアレイアンテナ回路、合成回路及び受信用フェーズドアレイアンテナ回路

【課題】入力信号を複数の信号に低損失で分配することができる分配回路を提供することを課題とする。

【解決手段】分配回路は、信号入力ノードに直列接続される複数のインダクタ(401〜40n+1)と、入力容量を有する入力端子及び出力端子を有し、前記複数のインダクタのそれぞれの間に前記入力端子が接続され、前記入力端子に入力される信号を増幅して前記出力端子から出力する複数の増幅素子(421〜42n)と、前記複数の増幅素子の出力端子と複数の信号出力ノードとの間にそれぞれ接続される複数の整合回路(431〜43n)とを有する。

(もっと読む)

21 - 30 / 397

[ Back to top ]