国際特許分類[H03F3/60]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 結合回路網が分布定数をもつ増幅器,例.導波管共振器をもつもの (397)

国際特許分類[H03F3/60]に分類される特許

11 - 20 / 397

リミッター回路

【課題】接続される低雑音増幅器の破壊を防止すると共に、この増幅器の飽和の範囲を狭くし正常動作の範囲を広くすることが可能なリミッター回路を提供すること。

【解決手段】一例のリミッター回路は、高周波入力端子に接続され、一定の飽和入力電力範囲を有する低雑音増幅器の入力端子と接地との間に接続されたPINダイオードと、前記低雑音増幅器の入力端子に一端を接続され他端は接地される、所定周波数の1/4波長の長さの伝送線路と、前記低雑音増幅器の入力端子に前記飽和入力電力範囲に入る信号が入力されるときに、前記伝送線路の他端と接地との間に、直列接続される電力設定用抵抗器及び定電圧電源を接続し、前記低雑音増幅器の入力端子に入る信号を、この範囲より電力の小さい正常入力電力範囲の信号に下げて前記低雑音増幅器の入力端子に入力する手段と、を有する。

(もっと読む)

F級増幅回路及びこれを用いた送信装置

【課題】基本波周波数の異なる複数の入力信号が入力する場合でも、各基本周波数に応じた高周波処理が行えるようにする。

【解決手段】 基本角周波数の異なる複数の信号をF級増幅し、該基本角周波数の信号成分及び、その高調波の信号成分を含んだ信号を出力するF級増幅器と、F級増幅器の後段に設けられて、当該F級増幅器に寄生する寄生回路のインピーダンスを取り込んで回路設定されることにより、信号の直流成分及び偶数次高調波の信号成分に対しては短絡状態とし、奇数次高調波の信号成分に対しては開放状態となる高調波処理部と、高調波処理部の後段に設けられて、高調波の信号成分に対しては短絡状態にする短絡部と、を備える。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

高周波加熱器

【課題】アンテナの負荷インピーダンスによらず、食品を高速に加熱すること。

【解決手段】制御部17で伝送線路15の長さのバラツキの影響を補正することによって、電力増幅器14の出力端での反射係数を高い精度で推測し、さらにその反射係数の値に従って予め用意された参照テーブルをベースにきめ細やかに電力増幅器14への入力電力を過剰に低下することなく制御することによって、高い精度で電力増幅器14の破壊や発振などを防ぎ、アンテナからの高周波出力を高いレベルに維持することが可能となる。

(もっと読む)

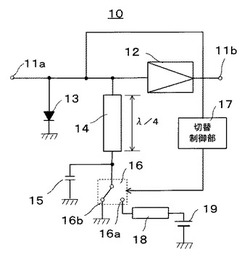

回路定数調整器及びそれを用いた低雑音増幅装置

【課題】 安定した発振抑制効果が得られると共に高精度に発振が抑制できるように回路定数が調整できるようにする。

【解決手段】 回路定数を調整する回路定数調整器16であって、終端が開放端に形成されたスタブ16eと、一端17bがスタブ16eに接続されると共に、他端17aが回路定数調整対象の回路12に接続され、かつ、抵抗値が設定可能に設けられた可変抵抗器16aと、可変抵抗器16aに制御信号を出力して、当該可変抵抗器16aの抵抗値を設定する抵抗値設定器16cと、を備える。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

電子回路

【課題】、高出力動作が可能なカレントリユース電子回路を提供すること。

【解決手段】第1端子、第2端子および制御端子を有し、前記第1端子が接地された第1トランジスタT1と、第1端子、第2端子および制御端子を有し、前記制御端子に前記第1トランジスタの第2端子が接続され、前記第1端子が前記第1トランジスタの前記第2端子と高周波的に接続され、前記第2端子に直流電源が接続される第2トランジスタT2と、前記第1トランジスタの第2端子と前記第2トランジスタの制御端子との間のノードに一端が接続され、他端が前記第2トランジスタの第1端子に接続された第1抵抗R1と、を具備した電子回路。

(もっと読む)

電力増幅回路

【課題】F級増幅器における効率を改善することができる電力増幅回路を提供する。

【解決手段】電力増幅回路は、予め定められた周波数の基本波を含む信号を増幅する増幅素子と、増幅素子が増幅した信号に含まれる基本波と、基本波の2倍波と、基本波の3倍波とそれぞれの特性インピーダンスとのインピーダンス整合をとる出力整合回路と、2倍波の反射位相を変化させる2倍波用チューナーと、3倍波の反射位相を変化させる3倍波用チューナーと、出力整合回路が出力する信号に含まれる基本波を通過させるとともに、信号に含まれる2倍波及び3倍波を反射する高調波反射フィルタであって、2倍波用チューナー及び3倍波用チューナーが接続され、2倍波用チューナー及び3倍波用チューナーを用いて2倍波及び3倍波の反射位相を独立に変化させる高調波反射フィルタとを備える。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

能動回路

【課題】2倍波処理回路の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得る。

【解決手段】バイアス回路5において、基本波整合回路4の出力側に接続され、基本波周波数成分を全通過させ、2倍波周波数成分を反射するフィルタ回路51と、基本波整合回路4の出力側とフィルタ回路51との間に接続され、基本波周波数で並列共振し、2倍波周波数に対してほぼ純抵抗となる2倍波吸収回路52と、2倍波吸収回路52に接続され、バイアス電圧を供給するバイアス電圧供給回路53とを備えた。

バイアス回路5において、2倍波周波数成分を高周波トランジスタ2側に反射させずに吸収することによって、2倍波処理回路3とバイアス回路5とで並列共振を起こすことがなく、その結果、2倍波処理回路3の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得ることができる。

(もっと読む)

11 - 20 / 397

[ Back to top ]