国際特許分類[H03H9/64]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | 電気機械的または電気音響的素子を含む回路網;電気機械的共振器 (8,923) | 濾波器 (961) | 弾性表面波を用いるもの (541)

国際特許分類[H03H9/64]に分類される特許

521 - 530 / 541

弾性表面波フィルタ

圧電基板(201)上に、第1のIDT(202)と第2のIDT(203)とを形成することにより構成され、第1のIDT(202)は入出力端子の一方

の端子(204)と入出力端子の他方の端子(205)との間、すなわち信号経路に直列に配置され、第2のIDT(203)は入出力端子の一方の端子(204)と第1のIDT(202)との間から信号経路に対して並列に配置される。さらに、第1のIDT(202)と第2のIDT(203)とはそれぞれの共振器により励起される弾性表面波の同一伝播路上で近接して配置される。

(もっと読む)

表面弾性波トランスデューサ

本発明は、これまでの公知の表面弾性波(SAW)トランスデューサに比べて伝搬特性の高いエッジ急峻度のもとで群遅延時間の周波数応答が格段に改善された表面波で作動するトランスデューサに関する。このトランスデューサは、SPUDTセルをベースに構成されており、この変換器構造においては2つのセルが設けられている。これらのセルは縦方向で異ならせてスケーリングを施される以外は同じようにデザインされている。スケーリングレベルに応じて音響波の局所フェーズは本発明のトランスデューサが用いられるフィルタの通過帯域における群遅延時間の周波数特性における脈動率が最大でも50nsとなるように作用する。  (もっと読む)

(もっと読む)

弾性表面波フィルタ、通信装置

【課題】小型化され、通過域の高周波側近傍の減衰量が改善された弾性表面波フィルタを提供する。

【解決手段】弾性表面波フィルタは、圧電基板上の入力側電極パッドと出力側電極パッドとの間に、複数の直列弾性表面波共振子および並列弾性表面波共振子が梯子型に配置されており、入力側電極パッドまたは出力側電極パッドの少なくとも一方を取り囲むように形成された接地電極パターンを前記圧電基板上に備える。

(もっと読む)

縦結合型弾性表面波共振子フィルタ

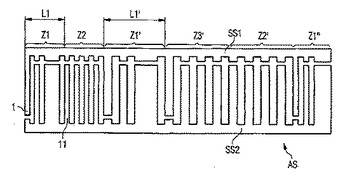

【課題】 通過帯域よりも高域側における不要スプリアスを効果的に抑圧することができる縦結合型弾性表面波共振子フィルタを得る。

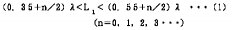

【解決手段】 水晶基板2上に第1,第2のIDT3,4が形成されており、第1,第2のIDT3,4が設けられている領域の表面波伝搬方向両側に反射器5,6が形成されており、第1,第2のIDTの隣接し合っている電極指3a1 ,4a1 の中心間距離L1 が下記の式(1)を満たすように構成されており、反射器5,6の各最も内側の電極指5a1 ,6a1 と、隣接するIDT3,4の最外側の電極指3a2 ,4a2 との間の電極指中心間距離L2 が下記の式(2)を満たすように構成されている縦結合型弾性表面波共振子フィルタ。

【数1】

【数2】 (もっと読む)

(もっと読む)

弾性表面波フィルタ、弾性表面波装置および通信装置

【課題】 通過帯域内の平坦度をより一層向上させた良好なフィルタ特性を有する、高品質な縦結合共振子型の弾性表面波フィルタを提供する。

【解決手段】 本発明では、上記圧電基板として回転YカットX伝搬LiTaO3 基板を用いるとともに、弾性表面波共振子を構成するIDT電極3におけるギャップ長Gを、弾性表面波の波長λの0.3倍以下に規定する(0.3λ≧G)。上記ギャップ長Gは、IDT電極3を構成する一対のバスバー31と、このバスバー31から対向方向に向かって延長される複数の電極指32…との間隔である。

(もっと読む)

弾性表面波フィルタ、弾性表面波装置および通信装置

トランスバーサル弾性表面波フィルタ

【課題】 トランスバーサル弾性表面波フィルタの帯域内特性を平坦化する手段を得る。

【解決手段】 圧電基板上に2つのIDT電極を所定の間隔をおいて配置したトランスバーサル弾性表面波フィルタであって、IDT電極の一方を反射機能を有する電極周期λRの基本区間と、反射機能を有しない電極周期λSの基本区間とを用いて形成すると共に電極周期λR及びλSを互いに異ならせる。

(もっと読む)

弾性表面波装置

【課題】この発明は、低損失、広帯域で急峻なスカート特性を要する弾性表面波装置を提供することを目的としている。

【解決手段】圧電性基板10上に、伝搬特性に方向性を有する一方向性電極構造のSPUDT3,4,7,8,11,12,14,15を互いに伝搬方向が逆方向になるように対向配置してなるRSPUDT5,9,13,16によって構成されるトランスデューサを、並列に接続している。

(もっと読む)

表面波反射器フィルタ

SAWフィルタ

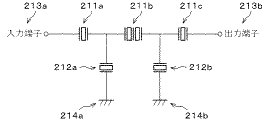

【課題】 通過帯域外の減衰量を大きくしたSAWフィルタを提供することを目的とする。

【解決手段】 圧電基板1上に三電極縦モード型SAWフィルタ素子4と、ラダー型フィルタ素子6を形成し、パッケージ9内に収納し、この三電極縦モード型SAWフィルタ素子4とラダー型SAWフィルタ素子6は縦続接続されており、三電極縦モード型SAWフィルタ素子4とラダー型SAWフィルタ素子6のアース端子14a,14b,14c,14dをパッケージ9のアース端子13a,13b,13c,13dとそれぞれ電気的に接続するとともに、アース端子13a,13b,13c,13dをパッケージ9内の一ヵ所において電気的に接続した構成である。

(もっと読む)

521 - 530 / 541

[ Back to top ]