国際特許分類[H03K17/16]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 混信電圧または混信電流を消去するための変形 (505)

国際特許分類[H03K17/16]に分類される特許

41 - 50 / 505

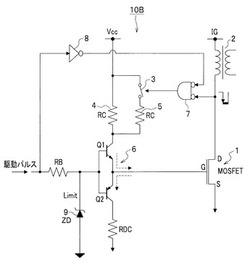

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

半導体装置

【課題】ハーフブリッジ回路のメインスイッチング素子が同時オンになることを確実に防止する。

【解決手段】ローサイド側の入力信号を遅延させてローサイド側遅延信号として出力する遅延回路20と、ハイサイド側の入力信号からハイサイド側セット出力信号と予備リセット信号とを生成して出力するパルス発生回路12と、ローサイド側の入力信号がアクティブになってからローサイド側遅延信号がアクティブになるまでの期間、又は予備リセット信号がアクティブである期間にハイサイド側リセット出力信号をアクティブにするリセット信号生成回路30と、を備えるハーフブリッジドライバとする。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

ゲート駆動回路

【課題】 簡便な回路構成で、高速に動作するゲート駆動回路を提供することである。

【解決手段】 パワー半導体素子のゲート端子に正電圧を印加するためのNPNトランジスタと、パワー半導体素子のゲート端子に負電圧を印加するためのPNPトランジスタと、NPNトランジスタと、PNPトランジスタとに直列に接続された遮断用抵抗器と、遮断用抵抗器に、正極がパワー半導体素子のゲート端子側となるように並列に接続された遮断用抵抗器切換え半導体スイッチとを備えたゲート駆動回路である。

(もっと読む)

半導体デバイス駆動回路及び半導体装置

【課題】電源電圧が変動しても半導体デバイスのオン動作及びオフ動作を安定して駆動できる半導体デバイス駆動回路を得る。

【解決手段】ドライブ回路10は、入力回路11より得られる制御信号S11に基づき、インバータG4から電源電圧VCCにより決定される“H”(オンレベル)、あるいは接地電圧GNDにより決定される“L”(オフレベル)の出力電圧VOUT1を駆動信号として半導体デバイスQ1のゲートに出力する。基準電源部14は抵抗R1及びR2の直列接続により、電源電圧VCC,接地電圧GND間の電位差を所定の分圧比率(抵抗R1及びR2による抵抗比)で分圧して得られる電圧が基準電圧VREF1として得られる。バッファ回路8は基準電圧VREF1により決定される基準信号となる出力電圧VOUT2を半導体デバイスQ1のソースに付与する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

スイッチング素子の駆動回路

【課題】オフ保持用スイッチング素子46をオフ状態とすべき期間において、この素子が誤ってオフ状態とされることに起因するスイッチング素子S*#の信頼性の低下を抑制することのできるスイッチング素子の駆動回路を提供する。

【解決手段】オフ保持回路48は、信号生成部26の操作信号INを入力としてゲートの充電処理の実行中であると判断された場合、オフ保持用スイッチング素子46をオフし、操作信号INを入力としてゲートの放電処理の実行中であると判断されて且つゲート電圧検出部50の出力信号GPRを入力としてゲート電圧Vgeが低いと判断された場合、オフ保持用スイッチング素子46をオンする。ここで、上記駆動回路は、ゲート電圧Vgeが閾値電圧を跨いでから出力信号GPRの論理が反転するまでの時間を、操作信号INを入力としてオフ保持回路48によって把握される充電処理指示時間の最小値以下とするように構成される。

(もっと読む)

41 - 50 / 505

[ Back to top ]