国際特許分類[H03K17/16]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 混信電圧または混信電流を消去するための変形 (505)

国際特許分類[H03K17/16]に分類される特許

31 - 40 / 505

スイッチ装置

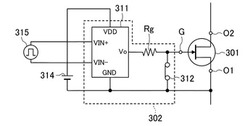

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体かなるスイッチング素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続されたコンデンサC1と抵抗R1とからなる並列回路と、並列回路にコンデンサC2とスイッチング素子Q2と抵抗R2からなる直列回路がさらに並列接続され、コンデンサC2とスイッチング素子Q2との接続点にダイオードD1のアノードが接続され、ダイオードD1のカソードとスイッチング素子Q2のゲートはスイッチング素子Q1のソースに接続され、制御信号のオフ信号に対してスイッチング素子Q1ゲートを負電位にバイアスする。

(もっと読む)

半導体装置

【課題】体格及びコストの増大が抑制された半導体装置を提供する。

【解決手段】直流電源とグランドとの間に直列接続された2つの単位回路と、単位回路を制御する制御部と、を備え、2つの単位回路の中点に誘導性負荷が接続された半導体装置であって、2つの単位回路それぞれは、第1スイッチ素子と、第1スイッチ素子と逆並列接続された還流ダイオードと、還流ダイオードと第1スイッチ素子それぞれと並列接続されたバイパス部と、を有し、バイパス部は、直列接続された第2スイッチ素子及び抵抗を有し、制御部は、2つの単位回路の第1スイッチ素子をOFF状態にするデッド期間を挟んで、2つの第1スイッチ素子を交互にON状態とし、デッド期間において、一方の第1スイッチ素子がOFF状態からON状態に移行するまで、一方の第1スイッチ素子と並列接続された第2スイッチ素子をON状態にする。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

スイッチング素子の駆動装置及びスイッチング素子の駆動方法

【課題】スイッチング損失の増大を抑制しつつ、より高い周波数帯で発生するスイッチングノイズを抑制できるスイッチング素子の駆動装置を提供する。

【解決手段】スルーレート調整部は、NチャネルMOSFETを介してDCモータに出力される電圧波形のスルーレートを変化させ、キャリア周波数によって決まる周波数帯よりも高い周波数帯域に現れるスイッチングノイズの周波数成分を分散させてピークレベルを低下させる。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

パワーMOSFETの駆動回路およびその素子値決定方法

【課題】パワーMOSFETを高速駆動する場合であっても、寄生インダクタンスに流れる電流の時間変化に応じて発生する電圧に起因したセルフターンオンの発生を防止できるようにしたパワーMOSFETの駆動回路、また、その素子値決定方法を提供する。

【解決手段】制御回路が、駆動回路によってスイッチを駆動制御することで、(2)区間においてスイッチS2HおよびS2Lをオンすると共にその他をオフとし、(3)区間においてスイッチS1LおよびS3Hをオンすると共にその他をオフとする。すると、(2)〜(3)区間にかけて、ハイサイド側のMOSFETのゲートソース間を所定のインピーダンスに切り替えることができ、リカバリー後半に至ったとしてもハイサイド側のMOSFETのゲートソース間電圧Vgs1を閾値電圧Vt未満に抑制できる。

(もっと読む)

半導体素子制御装置

【課題】駆動用半導体素子が意図せずに導通することを防止できる半導体素子制御装置を提供する。

【解決手段】駆動用トランジスタTr11は、一対の直流電源線13、14間に直流モータ12とともに直列に接続される。抵抗素子R13は、直流電源線13と駆動用トランジスタTr11のゲート端子との間に接続される。コンデンサC11および開路用トランジスタTr14の直列回路は、駆動用トランジスタTr11のゲート端子と直流電源線14との間に接続される。駆動制御回路15は、通常状態に設定されると、開路用トランジスタTr14をオンし、制御用トランジスタTr12、Tr13を通じて駆動用トランジスタTr11の導通状態を制御する。駆動制御回路15は、制御用トランジスタTr12、Tr13の双方がオフのとき、開路用トランジスタTr14をオフする。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

31 - 40 / 505

[ Back to top ]