国際特許分類[H03K17/16]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 混信電圧または混信電流を消去するための変形 (505)

国際特許分類[H03K17/16]に分類される特許

11 - 20 / 505

ドライバ及びその使用方法

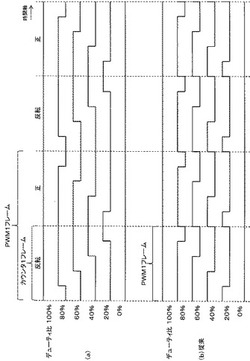

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

チョッパ型コンパレータ

【課題】動作時の貫通電流を低減させ、かつ動作スピードをあまり損なわないチョッパ型コンパレータを得る。

【解決手段】インバータと接地電圧端子間にNチャネル型MOSトランジスタ8を接続し、そのゲート端子に可変電圧源9を接続する。インバータと電源電圧端子間にPチャネル型MOSトランジスタ7を接続し、そのゲート端子に可変電圧源10を接続する。

(もっと読む)

スイッチ制御装置

【課題】互いにオンオフ状態が反転するように制御すべき2つのスイッチング素子の特性に応じて容易にデッドタイムを調整可能なスイッチ制御装置を提供する。

【解決手段】互いにオンオフ状態が反転するように制御する第1及び第2のスイッチング素子を備えるスイッチ制御装置であって、前記第1及び第2のスイッチング素子の内、一方のスイッチング素子に出力する制御信号をオフレベルに切替えた時点から、コンデンサの容量で設定される設定期間後に他方のスイッチング素子に出力する制御信号をオンレベルに切替える信号を出力する制御信号生成回路を備える。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

電力変換回路、多相ボルテージレギュレータ、及び電力変換方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】本発明による電力変換回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ11及びローサイドトランジスタ12と、ハイサイドトランジスタ11及びローサイドトランジスタ12のゲートを相補に駆動する2つの駆動回路21、22とを具備する。ハイサイドトランジスタ11はノーマリオフ型トランジスタであり、ローサイドトランジスタ12は、ノーマリオン型トランジスタである。

(もっと読む)

ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

(もっと読む)

11 - 20 / 505

[ Back to top ]