国際特許分類[H03K17/16]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 混信電圧または混信電流を消去するための変形 (505)

国際特許分類[H03K17/16]に分類される特許

51 - 60 / 505

スイッチング回路

【課題】スイッチング素子の動作に起因するノイズの大きさが低減された、小型で製造コストの低いスイッチング回路を提供する。

【解決手段】スイッチング素子と、一定周期でパルス波のドライバ信号を出力するドライバ信号出力回路と、ドライバ信号のパルス波の周期を複数含む一定期間内において駆動力を変化させながら、ドライバ信号の周期に同期してスイッチング素子を駆動する駆動回路とを備える。

(もっと読む)

負荷駆動装置

【課題】よりゲート電圧の傾きのバラツキを小さくすることで、スイッチング損失や電圧サージおよびピーク電流のバラツキを小さくする。

【解決手段】オフ保持デバイス5に対してオフ許可信号が禁止状態から許可状態に切り替わったことが伝わることを制御遅延演算回路6によって遅延時間だけ遅らせるようにする。これにより、遅延時間経過後に、既に定電流の狙い値まで達して安定した値になっている定電流駆動回路30の出力電流をスイッチング素子1のゲート1aに供給されるようにできる。したがって、ゲート電圧の立ち上がり傾きのバラツキを小さくすることができ、スイッチング損失や電圧サージおよびピーク電流のバラツキを小さくすることが可能となる。

(もっと読む)

スイッチング回路装置及びそれを有する電源装置

【課題】スイッチング時の電流の急激な変化を抑制しオン状態でのオン抵抗を抑制する。

【解決手段】電源回路内の第1のノードと第2のノードとの間に設けられるスイッチング回路装置であって,前記第1または第2のノードにインダクタが接続され,第1のノードと第2のノードとの間に設けられ第1のゲート幅を有する第1のトランジスタと,第1のノードと第2のノードとの間に第1のトランジスタに並列に設けられ第1のゲート幅より大きい第2のゲート幅を有する第2のトランジスタと,電源回路の出力電圧に応じて生成される制御信号に応答して,第1のトランジスタをオン,オフに駆動する第1の駆動信号と,第2のトランジスタをオン,オフに駆動する第2の駆動信号とを,時間的にずらして出力する駆動信号生成回路とを有する。

(もっと読む)

スイッチング装置、スイッチングモジュール

【課題】本発明は、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【解決手段】本発明にかかるスイッチング装置は、スイッチング素子1と、エミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることを特徴とする。

(もっと読む)

スイッチ回路及び半導体回路

【課題】 超音波診断装置等に適用され、送信信号または反射信号の電位変動に対しスイッチの誤動作や素子の破壊を起こすことなく、生体からの反射信号を広帯域、低雑音で受信回路に伝送するT/Rスイッチ回路を実現する。

【解決手段】 2つのMOSトランジスタのソースを共通に直列接続した共有ソース端子と、双方向スイッチ回路のゲート端子を共通に接続した共有ゲート端子と、2つのMOSトランジスタのドレインが入出力端子に接続されて構成される双方向スイッチ回路と、共有ゲート端子と共有ソース端子に接続され共有ソース端子の電位変動に対して共有ゲート端子の電位を同相で追従させ、スイッチのオンまたはオフ信号を共有ゲート端子に送るフローティングゲート電圧制御回路と、によりスイッチ回路を構成する。

(もっと読む)

誘導性負荷の駆動回路

【課題】スイッチング素子のオンオフによる誘導性負荷の電流応答性を良好なものとしながら駆動回路内の発熱をより抑制する。

【解決手段】誘導性負荷10を駆動する駆動回路20に、誘導性負荷10と並列接続され且つ互いに直列接続された第1の抵抗42および第2の抵抗44と、第2の抵抗44に並列接続されたコンデンサ46と、誘導性負荷10と並列接続されゲートが抵抗42と第2の抵抗44(コンデンサ46)との接続点に接続されドレインがグランドに接地されたNチャネル型のFET32と、FET32のソースと電源ライン24との間に介在しドレインからソースの方向を順方向とする第1のダイオード34とを設ける。

(もっと読む)

スイッチング回路

【課題】スイッチング回路のデッドタイム制御における電力効率を向上させる。

【解決手段】スイッチング制御部2は、パルス信号Aがロウレベルの時に、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち上がったのを検出してから、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち上がるように、スイッチング部Wを制御し、パルス信号Aがハイレベルの時に、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち下がったのを検出してから、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち下がるように、スイッチング部Wを制御する。

(もっと読む)

スイッチング回路装置及び制御回路

【課題】スイッチングトランジスタを適切にオフ動作する。

【解決手段】スイッチング回路装置は,高電位端子に接続されたドレインと低電位電源に接続されたソースとゲートとを有し,高電位端子と低電位電源との間に接続されたスイッチングトランジスタと,入力制御信号に応答して,スイッチングトランジスタのゲートにスイッチングトランジスタの閾値電圧より高い高電位と前記低電位電源の電位とを有する駆動パルスを出力する駆動回路とを有し,駆動回路は,スイッチングトランジスタのゲートとソースとの間に設けられた第1の駆動トランジスタを含む第1のインバータを有し,駆動パルスにより前記スイッチングトランジスタがオンからオフに変化するときに,第1の駆動トランジスタが導通してスイッチングトランジスタのゲートとソース間を短絡する。

(もっと読む)

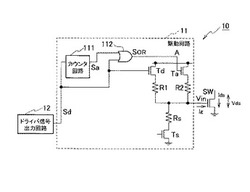

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

スイッチング回路およびスイッチング回路を用いた撮像装置

【課題】EM−CCDのCMG駆動回路からEM−CCDの出力信号への飛び込みを低減しながら、負荷容量CMG電圧の振幅の減衰を防ぎ、矩形波特性を改善する。

【解決手段】論理バッファとPchMOSとNchMOSのゲート間にフェライトビーズとダイオードの並列接続を挿入し、MOSがターンオフする方向にダイオードが接続されているスイッチング回路において、PchMOSのドレインソース間導通抵抗が2オーム以上あり、PchMOSのドレインとNchMOSのドレインとが1オーム以上の抵抗で接続され、PchMOSのドレインと容量負荷間に、スイッチング基本波周波数におけるインピーダンスがスイッチング基本波周波数における前記容量性負荷のインピーダンスの1/2より低いインピーダンスのフェライトビーズを直列接続する。

(もっと読む)

51 - 60 / 505

[ Back to top ]