国際特許分類[H03K23/54]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 計数連鎖を包含するパルス計数器;計数連鎖を包含する周波数分割器 (291) | ゲート信号またはクロック信号がすべての段に印加されるもの,すなわち.同期形計数器 (94) | 双安定再生トリガ回路を用いるもの (32) | リング計数器,すなわち,フイードバックシフトレジスタ計数器 (23)

国際特許分類[H03K23/54]に分類される特許

1 - 10 / 23

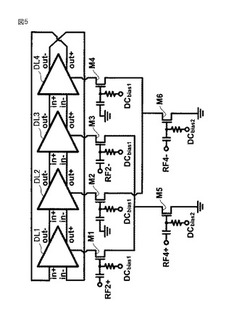

分周回路およびPLL回路

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジスタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトランジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

設定可能な分周比による周波数分周器

設定可能な分周比を使用する信号の周波数を分周する方法が開示される。第1周波数による入力信号は、設定可能な分周比による周波数分周器における、クロックドスイッチで受信される。周波数分周器内のノンクロックドスイッチは、複数の分周比の1つを選択するため、操作される。出力信号は、選択された分周比によって分周された第1周波数である第2周波数により出力される。  (もっと読む)

(もっと読む)

分周回路及び半導体装置

【課題】回路動作の安定性の向上と、消費電力の低減とを両立できるようにした分周回路及び半導体装置を提供する。

【解決手段】発振回路に近い前段の側にあって高い周波数で動作するFF回路10と、発振回路から遠い後段の側にあって低い周波数で動作するFF回路10と、を備え、前段と後段の各FF回路10は、分周回路の動作時に通常、オン、オフを繰り返すFB−SOI−MOSFET11〜14、21、25をそれぞれ有し、前段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth1│とし、後段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth2│としたとき、│Vth1│<│Vth2│に設定されている。

(もっと読む)

分周回路

【課題】 不要な周波数の信号の生成を抑制可能な分周回路を提供する。

【解決手段】 分周回路は、入力信号をクロック信号に同期して順次シフトする少なくともnビットのシフトレジスタと、シフトレジスタのnビットの出力信号のうち、入力信号をnビットシフトしたビットの出力信号の論理レベルの変化に応じて、入力信号をパルス状に変化させるパルス生成回路と、クロック信号をnビットのビット数に応じた分周比で分周するために、シフトレジスタの何れか1ビットの出力信号、または、入力信号の論理レベルの変化に応じて論理レベルが反転する分周信号を生成する分周信号生成回路と、を備える。

(もっと読む)

デュアルモジュラスプリスケーラ

【課題】セットアップマージンを増加させて、更なる高速動作を図る。

【解決手段】リング状にカスケード接続された9個のフリップフロップU12,U4〜U11、及びNANDゲートU3を備えている。フリップフロップU12,U4〜U11は、初段から最終段に向けてこの順で配列され、それぞれ、マスタースレイブ方式のフリップフロップにより構成されている。フリップフロップU12のマスターラッチに、分周比切替端子T−PSが接続されたNORゲートG1を組み込む。

(もっと読む)

パルス出力回路、表示装置

【課題】 一導電型のTFTによって構成され、かつ出力信号の振幅を正常に得られる表示装置の駆動回路を提供する。

【解決手段】 TFT101、104にパルスが入力されてONし、ノードαの電位が上昇した後、VDD−VthNとなったところで浮遊状態となる。よってTFT105がONし、クロック信号がHiとなるのに伴って出力ノードの電位が上昇する。一方、TFT105のゲート電極の電位は、出力ノードの電位上昇に伴い、容量107の働きによってさらに上昇し、VDD+VthNより高くなる。よって出力ノードの電位は、TFT105のしきい値によって電圧降下することなくVDDまで上昇する。その後、次段出力がTFT102、103に入力されてONし、ノードαの電位は下降してTFT105がOFFする。同時にTFT106がONし、出力ノードの電位はLoとなる。

(もっと読む)

シフトレジスタ

【課題】シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロック入力の立ち上がり(もしくは立ち下がり)エッジのみで動作可能とするシフトレジスタを提供する。

【解決手段】制御信号CK(36)がLで制御信号CKb(37)がHのとき、スイッチ12を経て入力信号D(11)はラッチセル13のインバータ14に加えられ、インバータ14の出力信号がラッチセル13の出力としてインバータ16で反転されてシフト出力Q0(17)となる。スイッチ18は制御信号CKb(37)が立ち下がる時点、すなわちクロック入力CK_in(34)の立ち上がり時点で動作してラッチセル13の出力を通過させ、ラッチセル19のインバータ20に加え、インバータ20の出力信号がラッチセル19の出力としてシフト出力Q1(22)となる。以下同様に、スイッチ23,29及びラッチセル24,30を経て入力信号D(11)がシフト出力Q2(28),Q3(33)に次々と伝搬される。

(もっと読む)

1 - 10 / 23

[ Back to top ]