国際特許分類[H03K5/007]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | DCレベルを変えるもの (34) | 基線の安定 (30)

国際特許分類[H03K5/007]に分類される特許

1 - 10 / 30

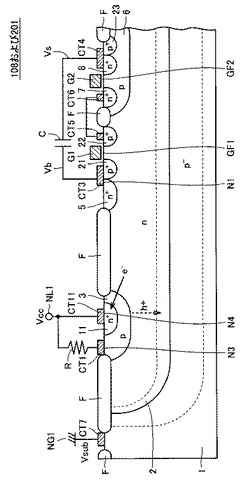

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

波形整形回路

【課題】 複数のツェナーダイオードを用いることによって、簡易な構成で、所望の波形に変換できる波形整形回路を提供する。

【解決手段】 オルタネータGからの出力信号に基づいて、矩形状に信号変換された矩形波信号を制御手段2へ出力する波形整形回路において、アノード側に接続されたオルタネータGからの前記出力信号が所定レベル以上の電圧である場合に、カソード側からの電源出力によってハイレベルに設定し、前記矩形波信号として制御手段2が検出可能に接続される第1のツェナーダイオード3と、アノード側に接続されたオルタネータGからの前記出力信号が所定レベルよりも低い電圧である場合に、アノード側の電源出力を、カソード側の接地によってローレベルに設定し、前記矩形波信号として制御手段2が検出可能に接続される第2のツェナーダイオード4と、を備えてなる。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

スイッチ両端の電圧を制限するためのシステム、方法、および装置

【課題】電圧クランプ回路構成を用いてスイッチ両端の電圧を制限するためのシステム、方法、および装置を提供する。

【解決手段】電圧クランプ回路構成125は、入力227および出力229を備えた整流器回路225であって、入力227は動作回路構成に渡って並列に連絡する整流器回路225と、整流器回路225の出力229と並列に連絡する電子能動スイッチング素子205と、電子能動スイッチング素子205と並列に連絡する少なくとも1つのツェナー・ダイオード210と、を備えていても良い。電子能動スイッチング素子205およびツェナー・ダイオード210に渡る電圧が所定の値を満たすかまたは超えた場合には、電流が電子能動スイッチング素子205を通って流れて、動作回路構成に渡る電圧を電圧クランプ回路構成125の電圧制限内に制限する。

(もっと読む)

比較回路

【課題】消費電流および回路規模をほとんど増大させることなく、容易に容量の充電時間を短くすることの出来る比較回路を提供する。

【解決手段】差動増幅回路10の出力が入力される単相増幅回路20の出力をNチャネルMOSトランジスタMN5からなるソースフォロワによるクランプ回路41に入力し、当該クランプ回路41により単相増幅回路20の入力を制限することにより、新たに定電圧源を設けることなく必要な充電電圧幅を狭めて容量Cpの充電時間を短くすることができる。また、単相増幅回路10の出力に応じて単相増幅回路10の入力を制限するので、単相増幅回路10の閾値電圧のばらつきや電源電圧の影響が問題にならない。

(もっと読む)

信号生成回路

【課題】回路に設けた容量をソフトスタート機能と共用可能でき、タイマ時間の設定の自由度が高くて精度の良いタイマ機能を実現可能な信号生成回路を提供する。

【解決手段】電流供給回路11から供給する電流Issを、回路に設けた共用する容量(Css)12に供給するとともに、差動増幅器21の比較入力としてクランプ回路20に加える。クランプ回路20は、容量(Css)12の電流供給回路11側端子電圧Vssとソフトスタート完了指示電圧Vc10を比較することにより、端子電圧Vssがソフトスタート完了電圧Vc1を上回った場合に、容量(Css)12に供給される電流Issを全て引き込むようしてクランプ機能を働かせる。クランプ回路20がクランプ作動状態に入る少し前に、差動増幅器21の出力Vo1が単相増幅器31のしきい値電圧Vtaを過ぎると、電流Issの切り替え(電流値Iss1から電流値Iss2への切り替え)が行われる。

(もっと読む)

レベルシフタ誤動作防止回路

【課題】本発明は、レベルシフタ誤動作防止回路に係り、レベルシフタの誤動作を、信号伝達の過大な遅延と消費電流の増大とを招くことなく防止することにある。

【解決手段】伝達すべき信号に応じて駆動されるN型トランジスタ30と、N型トランジスタ30の出力に応じて駆動されるP型トランジスタ32と、P型トランジスタ32を駆動するために設けられるプルアップ抵抗34と、を有する、基準電圧が互いに異なる2つの回路系の間で信号伝達を行うレベルシフタ16の誤動作を防止する回路において、2つの回路系の基準電圧が相対変位した際、N型トランジスタ30に存在する寄生容量36へプルアップ抵抗34を介して充電電流が供給される前に、その寄生容量36へ充電電流を供給する急速充電手段を設ける。

(もっと読む)

ドライブ回路

【課題】低電圧の制御信号を高電圧の制御信号に変換して出力する高圧用のドライブ回路において、待機時の消費電力を削減することができるようにする。

【解決手段】低圧部1からの制御信号a1〜d1及びa2〜d2により高圧部2のトランジスタMN1〜MN8を駆動し、操作対象3に駆動信号を出力する。その際、低圧部1からの制御信号a1〜d1をそれぞれ論理積ゲートQ1〜Q4の一方の入力端子を介して高圧部2のトランジスタMN1,MN3,MN5,MN7のゲートに入力し、論理積ゲートQ1〜Q4の他方の入力端子には高圧部2のオン/オフ信号を入力する。

(もっと読む)

単位回路および電子回路

【課題】出力回路における各トランジスタのゲート・ソース間に印加される電圧を制限するための構成や単位回路へ入力される制御信号の振幅を小さくするための構成を簡素化する。

【解決手段】単位回路Jは、電源線101と接地線103との間に直列に接続された第1のPチャネルトランジスタ、第2のPチャネルトランジスタ、第1のNチャネルトランジスタ、および第2のNチャネルトランジスタとを備える。そして、第1のPチャネルトランジスタがオン状態のときにその電位がVDDとなり、第1のPチャネルトランジスタがオフ状態のときにその電位がVREF+Vtp2となる第1出力信号V1を第1出力端子から出力し、第2のNチャネルトランジスタがオン状態のときにその電位がGNDとなり、第2のNチャネルトランジスタがオフ状態のときにその電位がVREF−Vtn1となる第2出力信号V2を第2出力端子から出力する。

(もっと読む)

信号レベル変換回路および位相同期回路

【課題】信号レベル変換回路の上限動作周波数を向上させる。

【解決手段】クロック信号をゲート(G)電極に受ける第1MOSトランジスタ(MOS−Tr)と,ドレイン(D)電極を第1MOS−TrのD電極に接続される第2MOS−Trと,逆相のクロック信号をG電極に受ける第3MOS−Trと,G電極およびD電極を第2MOS−TrのG電極と第3MOS−TrのD電極に接続された第4MOS−Trと,第1および第2MOS−TrのD電極から取り出した信号を受けるインバータ回路により構成されたレベル変換回路において,第2MOS−Trのソース電極と電源の間,または,第4MOS−Trのソース電極と電源の間の少なくとも一方に,並列に接続した複数の第5MOS−Trを設け,インバータ回路の出力の平均電圧が低電位側の電源と高電位側の電源の中間の電圧になるように第5MOS−Trの導通及び遮断を制御する制御回路を設ける。

(もっと読む)

1 - 10 / 30

[ Back to top ]