国際特許分類[H04L1/00]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | 受信情報中の誤りを検出または防止するための配置 (3,742)

国際特許分類[H04L1/00]の下位に属する分類

ダイバーシチ受信によるもの (16)

送信の繰り返しによるもの,例.ベルダン方式 (78)

帰路チャネルを用いるもの (1,269)

信号品質検出器を用いるもの (156)

信頼性を増すために冗長な装置を用いるもの (159)

訂正動作を試験するもの (11)

国際特許分類[H04L1/00]に分類される特許

81 - 90 / 2,053

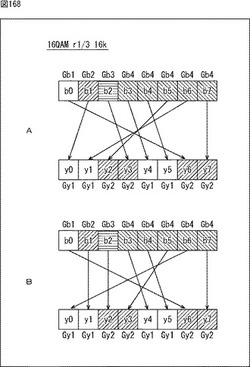

データ処理装置、及び、データ処理方法

【課題】データのエラーに対する耐性を向上させる。

【解決手段】デマルチプレクサは、DVB-S.2の符号長が16200ビットで、符号化率が1/3のLDPC符号を16QAMで変調する場合に、4×2ビットの符号ビットと、連続する2個のシンボルの4×2ビットのシンボルビットの最上位ビットからi+1ビット目を、それぞれ、ビットb#iとy#iとすると、例えば、b0はy6に、b1はy0に、b2はy3に、b3はy4に、b4はy5に、b5はy2に、b6はy1に、b7はy7に、それぞれ割り当てる入れ替えを行う。本技術は、例えば、LDPC符号を伝送する伝送システム等に適用できる。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DVB−HシステムのMPE−FECフレームのデコーディングのための内蔵SRAMのサイズを小さくする。

【解決手段】集積回路3は、TSIF31、RSデコーダ32、内蔵SRAM33、DRAMインターフェース34、中央処理ユニット35を具備する。TSIF31はDVB−HシステムのMPE−FECフレームを含んだTSパケットを受信して、IPデータグラムを含んだMPEセクションとパリティーデータを含んだMPE−FECセクションを抽出して、MPEセクションとMPE−FECセクションの第1テーブルと消去ビットマップテーブルの第2テーブルがDRAM4に生成される。内蔵SRAM33には、DRAMのバースト転送によってDRAMの第1と第2のテーブルの一部の格納データが格納される。RSデコーダ32が内蔵SRAM33をアクセスして、一部の格納データを使用してリード・ソロモン・デコーディングを実行する。

(もっと読む)

試験装置及び試験方法

【課題】IC,LSIやそれらを含む装置等を試験対象部として試験を行う試験装置及び試験方法に関する。

【解決手段】測定制御部3により制御されるPRBS発生部1と、このPRBS発生部1からのPRBS信号を試験信号として試験対象部4に入力し、この試験対象部4から出力されたPRBS信号の正常性を検査するPRBS検出部2とを備え、PRBS発生部1は、PRBSパターン信号にPRBSパターンのヘッダーを付加した試験信号を出力して前記試験対象部4に入力する構成を有し、PRBS検出部2は、試験対象部4から出力された試験信号のヘッダーを検出し、このヘッダーのパターンに従ったPRBS比較パターンを発生して、試験対象部4から出力されたPRBSパターンの試験信号と照合する構成及び処理過程を有する。

(もっと読む)

通信処理システム、データ処理方法、送信装置、受信装置及びデータ処理プログラム

【課題】ブロック単位で誤り訂正が行われるデータの受信側において、キャッシュの高いヒット率を維持して、高速な誤り訂正処理を実現する、通信処理システム及びデータ処理方法を提供する。

【解決手段】通信処理システムは、データブロックを単位に誤り訂正処理されるデータをデータシンボルに分割して送信する送信手段と、データシンボルを受信してキャッシュメモリに保持しデータを再構成する受信手段とを備える。送信手段はキャッシュメモリの容量以下の大きさのデータシンボルを所定の順番に並べ替える第1の並べ替え手段を有し、受信手段はキャッシュメモリに保持されたデータシンボルのうち所定のデータブロックに属するデータシンボルに対して誤り訂正処理を実行する誤り訂正手段と、訂正処理を実行されたデータシンボルを所定の順番に基づいて並べ替える第2の並べ替え手段とを備える。

(もっと読む)

データフレームの再送信減少方法及びこのための受信ノード

【課題】データフレームの再送信減少方法及びこのための受信ノードを提供する。

【解決手段】前記方法は、(a)K個のソースデータをイレージャーコーディング(Erasure Coding)技法によりエンコーディングしたN個のデータフレームを連続的に受信する段階と、(b)受信されたN個のデータフレームのエラーを検査する段階と、(c)検査結果、エラーのないデータフレームの個数(R)が前記ソースデータの個数(K)以上の場合、復旧可能を知らせるACKメッセージを送信し、エラーのないデータフレームの個数(R)がソースデータの個数(K)未満の場合、再送信を要請するデータフレームの個数(X)を含むACKメッセージを送信する段階と、を含むことによって、データフレームのうち一部にエラーのある場合にも再送信要請をすることなくデータを復元することができる効果がある。

(もっと読む)

メディアコンバータ、及び、中継システム

【課題】物理レーンの一部に障害が発生しても、他のメディアコンバータに管理情報を通知するメディアコンバータ、及び、中継システムを提供する。

【解決手段】分配・制御ブロック挿入部64は、複数のPCSレーン1〜4に対し、データブロック0〜7を巡回的に分配するとともに、制御ブロック76を挿入し、データブロック0〜7及び制御ブロック76をそれぞれ含む複数のブロック列を形成する。そして、分配・制御ブロック挿入部64は、制御ブロック76を挿入する際、制御ブロック76の一部として、管理情報84を挿入する。

(もっと読む)

送信側通信装置及び再送制御方法

【課題】従来の受信側通信装置の構成を変更することなく、初送時とは異なる変調・符号化方式(MCS)を再送時に使用できるようにする。

【解決手段】適応変調・符号化(AMC)とハイブリッド自動再送制御(HARQ)とをサポートする無線通信システムにおいてパケットを受信側通信装置に送信する送信側通信装置の再送制御方法は、第1のMCSを使用して初送パケットを受信側通信装置に送信するステップ(S110〜S125)と、第1のMCSとは異なる第2のMCSを再送時に使用する場合(ステップS150;NO)、受信側通信装置において初送パケットと合成される再送パケットの送信に代えて、第2のMCSを使用して、該再送パケットにより伝送すべき再送データを含んだ新たな初送パケットを受信側通信装置に送信するステップ(ステップS155)と、を有する。

(もっと読む)

受信回路及びエラー検出方法

【課題】設計時のタイミング調整を容易とする受信回路及びエラー検出方法を提供すること

【解決手段】本発明にかかる受信回路は、位相の異なる複数のクロックを用いて、矩形波としてデータが遷移する受信シリアルデータビット列をサンプリングして、前記サンプリングされた受信シリアルデータビットを用いて受信データビット列を生成するDL回路部1と、前記サンプリングされた前記受信シリアルデータビットのうち、所定期間内に位相の異なるクロックを用いてサンプリングされた前記受信シリアルデータビットの値が一致するか否かを比較した結果に基づいて前記受信データビット列のエラー区間を検出するPD回路部2と、を備えるものである。

(もっと読む)

デジタルデータを符号化するための方法、デジタル信号を復号するための方法、デジタルデータを符号化するための装置、デジタル信号を復号するための装置、および集積回路

【課題】プラスチック光ファイバを通してデジタルデータを伝送するための有効な符号化および変調システムを提供する。

【解決手段】デジタルデータは3レベル剰余類コーディングによって符号化される。第1のレベルは、デジタルデータにバイナリBCHコーディングを施し、配置マッピングおよび格子変換によって剰余類分割を行なう。第2のレベルは別のバイナリBCHコーディングを施し、実質的に同じコードレートを有し、異なるサイズのコードワードで動作する2つのBCHコードによって、所望の構成に従い選択的に行なう。第3のレベルは符号化されない。第2および第3のレベルは、マッピングおよび格子変換を経る。レベルを加算した後、第2段格子変換を行なって、ゼロ平均配置を得る。3レベル剰余類コーダから出力されるシンボルはさらに変調される。

(もっと読む)

無線通信システムにおける無線資源割り当て方法

【課題】本発明は、無線通信システムでの無線資源割り当て方法に関するものである。

【解決手段】無線通信システムにおけるユーザ装置でデータを受信する方法であって、第1のスケジューリング情報をネットワークから受信して第1のスケジューリング情報に基づいて初期パケットをネットワークから受信し、ユーザ装置が初期パケットの正常なデコーディングに失敗した場合、NACKをネットワークに送信し、第2のスケジューリング情報をネットワークから受信して第2のスケジューリング情報に基づいて再送信パケットをネットワークから受信し、再送信パケットを初期パケットと組み合わせて、初期パケットおよび再送信パケットに関連するパケットを復元し、第1のスケジューリング情報および第2のスケジューリング情報のそれぞれは、スケジューリング情報がC−RNTIまたはSPS−C−RNTIのいずれかを有するように構成する。

(もっと読む)

81 - 90 / 2,053

[ Back to top ]