セイコーエプソン株式会社により出願された特許

49,201 - 49,210 / 51,324

圧電素子、圧電アクチュエーター、圧電ポンプ、インクジェット式記録ヘッド、インクジェットプリンター、表面弾性波素子、周波数フィルタ、発振器、電子回路、薄膜圧電共振子、および電子機器

【課題】 良好な圧電特性を有する圧電素子を提供する。

【解決手段】 本発明に係る圧電素子1は,

基板2と、

基板2の上方に形成されたバッファ層5と、

バッファ層5の上方に形成された、ペロブスカイト型構造を有する圧電体層6と、を含み、

バッファ層5は、導電性を有し,c軸(001)に優先配向しているビスマス系層状ペロブスカイト構造化合物からなる。

(もっと読む)

エッチング方法

【課題】 レジスト膜を露光する際のDOFマージンをある程度広く確保しつつ、反射防止膜に起因する問題を無くすことができるようにしたエッチング方法を提供する。

【解決手段】 シリコン基板1に形成されたシリコン酸化膜3上に直接レジスト膜5´を形成し、このレジスト膜5´を直接露光し、現像処理してレジストパターン5を形成する。次に、レジストパターン5をAr,O2,C4F6からなる混合ガスを用いてプラズマ処理して整形する。そして、この整形されたレジストパターン5をマスクにシリコン酸化膜3をエッチングしてコンタクトホール13を形成する。

(もっと読む)

固体撮像装置

【課題】余剰電荷の排出のための占有面積を縮小すると共に、設計の自由度を向上させる。

【解決手段】 基板上に複数のセンサセルがマトリクス状に配置されたセンサセルアレイを含む固体撮像装置であって、各センサセルは、前記基板内に設けられ、入射した光に応じた光発生電荷を発生させる光電変換素子2と、前記光電変換素子に隣り合って配置され、環状ゲートを有する出力トランジスタTmと、前記光電変換素子と前記出力トランジスタとの間に配置され、前記光電変換素子において発生した光発生電荷の転送を制御すると共に、前記光電変換素子からの光発生電荷を保持可能な電荷保持領域を有する転送・保持手段22と、前記ゲート下方の前記基板内に形成された高濃度不純物領域であって、前記光電変換素子において発生した光発生電荷が前記転送・保持手段から転送され、転送された光発生電荷を保持して前記出力トランジスタの閾値を変化させるキャリアポケット7と、前記光電変換素子において発生した余剰電荷を前記キャリアポケットに流す余剰電荷排出経路14と、を含む。

(もっと読む)

半導体基板の洗浄方法及びその装置

【課題】 処理液の供給を工夫することにより、半導体基板の面内にて均一に処理を行うことができる。

【解決手段】 液面レベルが下限位置LLに達するまでの間、流量調節弁の流量をポンプによる流量よりも徐々に大きくし、液面レベルが上限位置に達するまでの間、流量調節弁の流量をポンプによる流量よりも徐々に小さくする。このように各部を調整することにより、内槽3に貯留している処理液の液面レベルを上下動させる。これにより、液面レベルが半導体基板Wの面に沿って上下するので、処理における半導体基板Wの面内均一性をさらに高めることができる。

(もっと読む)

半導体基板乾燥装置

【課題】 周囲に飛散する水滴の跳ね返りを防止することにより、半導体基板の表面における水滴の残渣の発生を防止することができる。

【解決手段】 チャンバ1の内壁と回転保持部3との間に、回転保持部3を囲う吸収体7を備えている。したがって、半導体基板Wから周囲に飛散した水滴等は、多孔質部材である吸収体7に吸収されるので、周囲に飛散する水滴等の半導体基板Wへの跳ね返りが防止できる。その結果、乾燥処理による水滴の残渣の発生を防止できる。

(もっと読む)

多層配線基板、半導体装置、半導体基板、半導体装置の製造方法、電気光学装置及び電子デバイス

【課題】 絶縁膜形成用の液体材料の使用量を最小限に抑えることが可能な技術を提供する。

【解決手段】

基板110の上に複数の半導体膜310A、310Bを形成した後、液滴吐出法を用いて各半導体膜310A、310Bと重なる領域に、局所的にゲート絶縁膜形成用の液体材料を配置する。このように配置した液体材料を例えば100℃〜200℃程度の温度で乾燥し、さらに350℃〜400℃の温度で60分程度焼成することで、各半導体膜310A、310Bと重なる領域に局所的に形成されたゲート絶縁膜320A、320Bを得る。

(もっと読む)

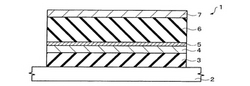

有機エレクトロルミネッセンス装置、有機エレクトロルミネッセンス装置の製造方法、電子機器

【課題】 発光特性の高効率化、及び長寿命化を達成し、諧調コントロールが容易になる有機エレクトロルミネッセンス装置を提供する。

【解決手段】 本発明の有機エレクトロルミネッセンス装置は、電極間に発光機能部7のみを有し、前記発光機能部7は、発光材料からなる第1機能部7bと、正孔注入/輸送材料からなる第2機能部7aと、これら第1機能部7b及び第2機能部7aの間に発光材料及び正孔注入/輸送材料が混在する中間部7cとを有してなることを特徴とする。

(もっと読む)

半導体装置の製造方法、電気光学装置及び電子デバイス

【課題】 高価で精密な露光装置及びエッチング装置を用いることなく、性能の高い半導体装置を製造することができる半導体装置の製造方法等を提供する。

【解決手段】 酸化シリコン膜12上に形成した微細孔13の中に単結晶シリコンからなる微粒子20を少なくとも1つ配置し、この上にアモルファスシリコン膜21を形成する。その後、アモルファスシリコン膜21の上方からレーザ光を照射し、シリコン微粒子を核として結晶成長させることにより、大きな粒径を有する略単結晶状態のシリコン膜14を形成する。そして、この略単結晶状態のシリコン膜14の少なくとも一部にチャネル領域が収まるようにTFTを形成する。

(もっと読む)

ゲート絶縁膜の形成方法、半導体装置、電気光学装置及び電子デバイス

【課題】 表面が平坦かつ均一な膜厚のゲート絶縁膜等を形成することができる技術を提供する。

【解決手段】 液体材料を複数回塗布することによってゲート絶縁膜を形成する。具体的には、パターンサイズの異なる半導体膜202A、202Bが形成された基板11上にゲート絶縁膜を形成するための液体材料を塗布し、これを焼成することによって第1ゲート絶縁膜220を形成する。第1ゲート絶縁膜220を形成することによって半導体膜表面と基板表面との間に生じた段差を小さくした後、この第1ゲート絶縁膜220の上に更に液体材料を塗布し、焼成することによって第2ゲート絶縁膜230を形成する。

(もっと読む)

電子部品及び半導体装置

【課題】チップ同士又はチップと回路基板と接合において、コストの削減又は信頼性の向上を図ることのできる電子部品及び半導体装置並びにこれらの製造方法並びにこれらを実装した回路基板及びこの回路基板を有する電子機器を提供する。

【解決手段】本発明は、チップ同士又はチップと回路基板と接合において、コストの削減又は信頼性の向上を図ることのできる集合型の半導体装置である。この集合型の半導体装置は、電極16を有する半導体チップ12と、半導体チップ12の上に設けられる応力緩和層14と、電極16から応力緩和層14の上にかけて形成される配線18と、応力緩和層14の上で配線18に形成されるハンダボール19と、を有する第1の半導体装置10と、第1の半導体装置10に電気的に接合される第2の半導体装置としてのベアチップ20と、を有する。

(もっと読む)

49,201 - 49,210 / 51,324

[ Back to top ]