三菱電機株式会社により出願された特許

1,021 - 1,030 / 33,312

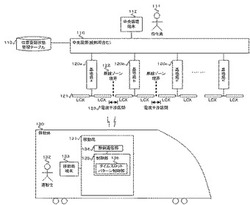

中央装置、及び移動局

【課題】時分割多元接続方式の無線通信システムにおいて、隣接する基地局間で同一の周波数を用いる場合に、隣接基地局間の無線ゾーン境界付近に発生する電波干渉による無線通信品質の劣化を抑制する。

【解決手段】通信フレームの所定の位置の第一のタイムスロットを用いて移動体が存在する現通信エリアに対応する基地局である現基地局を介して下り通信データを送出し、通信フレームの前記所定の位置と異なる位置の第二のタイムスロットを用いて現通信エリアに隣接する隣接通信エリアに対応する基地局である隣接基地局を介して前記下り通信データを送出し、現基地局を介する前記第二のタイムスロットを用いた通信、及び隣接基地局を介する前記第一のタイムスロットを用いた通信を禁止する。

(もっと読む)

無線通信装置および無線接続方法

【課題】接続相手機器に対して接続できない要因および解決案を提示することができる無線通信装置を得ること。

【解決手段】接続相手機器2との間で所定の無線通信処理を行う無線通信部11と、接続相手機器2との間の接続失敗要因と解決方法とを対応づけた情報である要因別解決方法DB17と、接続相手機器2との無線接続に失敗した場合に、接続失敗要因を判定する接続失敗要因判定部13と、要因別解決方法情報DB17に基づいて判定した接続失敗要因に対応する解決方法を抽出してユーザに提示する接続失敗要因および解決方法提示部15と、を備える。

(もっと読む)

ブートストラップ回路、半導体装置

【課題】ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供する。

【解決手段】ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。

(もっと読む)

マルチ画面コンテンツ表示システム、表示制御端末、オフセット時間生成装置、表示制御コマンド送信装置およびマルチ画面コンテンツ表示方法

【課題】外部同期信号等の同期専用の高価なH/Wを用いずに、従来方式より高精度な画面間同期を実現する。

【解決手段】全表示制御端末4からのVsyncの発生時刻に基づきオフセット時間を算出するオフセット時間生成装置2と、コンテンツデータを示す識別情報および表示開始指示時刻を含むコマンドを各表示制御端末に送信する表示制御コマンド送信装置3とを備え、表示制御端末4は、時刻同期サーバ装置1と内部時計を同期させる時刻同期クライアント手段41と、識別情報に基づき該当コンテンツデータを取得する表示準備手段43と、オフセット時間および表示開始指示時刻に基づく表示開始予定時刻を経過した後、表示開始指示を行う表示予定時刻待機手段44と、表示開始指示に従い、Vsync毎にコンテンツデータに基づく画像データを生成する表示処理手段45と、生成された画像データをVsync毎に表示装置5に出力する表示出力手段46とを備えた。

(もっと読む)

アンテナ装置

【課題】 ベースプレートの上方のみにカウンタウエイトを設ける構成を廃して、重心をより下げ、カウンタウエイトの配置の自由度が高いアンテナ装置を提供することを目的とする。

【解決手段】 ベースプレート部と、このベースプレート部上に形成されたアンテナ部と、前記ベースプレート部の下方に配置され、前記ベースプレート部にぶら下がったカウンタウエイト部とを備え、前記ベースプレート部は、前記アンテナ部、及び、前記カウンタウエイト部を支持する第1のベースプレート部と、この第1のベースプレート部と連結された第2のベースプレート部とを具備するものである。

(もっと読む)

移動体通信システム、基地局および移動端末

【課題】パーシステントスケジューリングは、初期送信時に基地局2がリソースアロケーションを移動端末3に送信すると、基地局2はある期間そのリソースアロケーションを用いて移動端末3にリソースを割り当てる。しかし、トーク時と無音時で通信するデータ量が異なるので、トーク時から無音時に移行した場合にはリソースの無駄が生じる。

【解決手段】本発明は、パーシステントスケジューリングを用いた場合、トーク時から無音時に移行することを検出すると、無音時のリソースを無音時専用チャネルに割り当てるとともに、トーク時に移動端末に割り当てていたリソースを開放することとしたので、リソースの無駄な割り当てを削減でき、システムとしてのスループット向上を図ることができる。

(もっと読む)

変圧器保護継電器

【課題】遮断器の開放後に発生する振動性共振電流が変圧器の一端のCTだけに流れても不要動作を回避することができる変圧器保護継電器を得る。

【解決手段】比率差動演算回路6と、差電流ID中の第2調波成分Icを検出して差電流ID中の基本波成分の実効値Ibに対する第2調波成分Icの割合が所定の割合以上であるか否かを判定する第2調波含有検出回路9と、基本波成分の実効値Ibに対する高周波の実効値Idの割合が所定の割合(C)以上であるか否かを判定する高調波含有検出部30と、遮断器CB開放後に演算された差電流IDを超えることがない所定の値未満であるか否かを判定する不足電流演算回路14と、高調波含有検出部30で所定の割合(C)以上であると判定され、かつ、不足電流演算回路14で所定の値(D)以下であると判定されたとき、比率差動演算回路6からの出力に対して限時動作を行うオンディレイ回路18とを備える。

(もっと読む)

保護継電システム

【課題】入力変換器本体を冗長化することシステムの信頼性を向上させることが可能な保護継電システムを得る。

【解決手段】IED5は、複数の入力変換器の組み内の入力変換器に異常が検出された場合、異常が検出された入力変換器からの第1のデジタルデータに代えて異常が検出されていない入力変換器からの第2のデジタルデータと、異常が検出されていない入力変換器からの第1のデジタルデータとを用いて電力系統の保護演算を行う。

(もっと読む)

半導体装置

【課題】パワー半導体素子の保護を確保できるように改善された半導体装置を提供する。

【解決手段】 半導体装置10は、いわゆるインテリジェントパワーモジュール(Intelligent Power Module、IPM)であり、その内部にパワー半導体素子12a〜12fを備えている。半導体装置10には、HVIC20およびLVIC30が設けられている。HVIC20は、高耐圧IC(High Voltage IC)であり、ハイサイド側にあるパワー半導体素子12a、12b、12cを駆動する駆動ICである。LVIC30は、低耐圧IC(Low Voltage IC)であり、ローサイド側にあるパワー半導体素子12d、12e、12fを駆動する駆動ICである。HVIC20は、Fo入力端子を備えている。LVIC30からFo入力端子への異常信号の入力に応じて、その信号を受け取ったHVIC20がパワー半導体素子12a、12bおよび12cをオフとする。

(もっと読む)

回転電機の積層鉄心、及び回転電機の積層鉄心の製造方法

【課題】歪みの発生を抑制することができ、かつ容易に製造することができる回転電機の積層鉄心、及び回転電機の積層鉄心の製造方法を得る。

【解決手段】鉄心本体11は、複数のコアブロック同士を環状に連結して構成されている。各コアブロック10は、複数枚のコア片33が軸線方向へ積層されて構成されている。コアブロック10同士の連結部のうち少なくともいずれかは、一方のコアブロック10のコア片33に設けられた連結用端部34aと、他方のコアブロック10のコア片33に設けられた連結用端部34aとが軸線方向へ交互に重なり、かつ互いに重なる連結用端部34a同士が連結軸37を中心に回動可能に連結された回動連結部とされている。各連結用端部34aには、鉄心本体11の外周側へ開放され、軸線方向へ並ぶことにより係止溝を形成する凹部38が設けられている。係止溝には、回動防止ピン41が挿入されている。

(もっと読む)

1,021 - 1,030 / 33,312

[ Back to top ]