ラピスセミコンダクタ株式会社により出願された特許

21 - 30 / 898

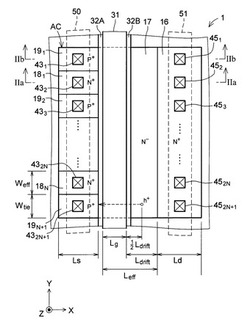

半導体装置

【課題】耐圧の低下を抑制しつつ電流駆動能力の向上と小型化とを実現できる半導体装置を提供する。

【解決手段】半導体装置1は、SOI基板の半導体層の上面に沿って形成されたゲート電極31と、ソース拡散領域181〜18Nと、電荷収集領域191〜19N+1と、ドレイン拡散領域16と、電界緩和領域17とを備える。ソース拡散領域181〜18Nと電荷収集領域191〜19N+1とは、Y軸方向に沿って交互に配列されている。ソース拡散領域181〜18Nの各々の幅をWeffとし、ゲート電極31の長さをLgとし、ゲート電極31とドレイン拡散領域16との互いに対向する端部間の距離をLdriftとするとき、Weff/2≦Lg+Ldrift/2、との関係式が成立する。

(もっと読む)

画像表示パネルドライバ

【課題】画像表示パネルに供給されるべき輝度電位の精度悪化を軽減でき且つサイズを小さくすることができる画像表示パネルドライバを提供する。

【解決手段】複数の階調電位を生成する階調電位生成部と、順次供給される画像データに基づいて当該複数の階調電位を順次選択するデコーダと、当該選択された階調電位に基づいて輝度電位を生成してこれを画像表示パネルに供給する駆動部と、当該画像データを構成する複数桁のビットのうちの少なくとも1つの桁のビットを制御ビットとして抽出する抽出部と、を含み、当該駆動部は当該輝度電位の高さを当該制御ビットに応じて調整する。

(もっと読む)

半導体装置の製造方法

【課題】良好な特性の確保、素子サイズの増加の回避、及び製造プロセスの簡素化を実現できる半導体装置の製造方法を提供する。

【解決手段】Si基板111の主面に、LOCOS酸化膜112bを含む酸化膜112を形成する工程と、Si基板111の主面の側に、ソース・ゲート形成領域113aとドレイン形成領域113bとを形成する工程と、レジスト116をマスクとして、Si基板111の主面の側のLOCOS酸化膜112bで覆われていないトレンチ114を通してイオン117注入を行い、イオン注入層118を形成する工程と、LOCOS酸化膜112b上及びソース・ゲート形成領域113a上を部分的に覆うようにゲート電極119を形成する工程とを有し、イオン注入層118のゲート電極119側の端部とゲート電極119のイオン注入層118側の端部との間に間隔121が存在するように、各工程を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

ファイル共有方法

【課題】 従来のCIFSプロトコルやFTPプロトコルを用いる方法では、ネットワークの管理ポリシーの観点から、同一ユーザに対するファイルアクセスにおいて、特定のネットワークからはRead/Writeを許可するが、別のネットワークからはReadのみでWriteは許可しない場合、それを実現することが出来なかった。

【解決手段】 第1のLAN環境に接続されている端末PC群から第2のLAN内のファイルにアクセスする場合に、前記端末PC群から発行されたURLに対応する前記ファイルサーバ上のデータ領域を前記Webサーバ上の前記仮想ディレクトリにマウントし、該マウントしたデータ領域を前記端末PC群から読み取ることにより第2のLAN環境から第1のLAN環境にのみファイルを転送可能とする。

(もっと読む)

ROMテスト時間の短縮方法

【課題】 従来の技術においては、ROM3個分のテスト時間を2個分のテスト時間までしか短縮できないという問題、或いは、加算或いは減算をおこなうため、データビット数の変動の虞があると共に、信頼性が低下する虞があった。

【解決手段】 複数個のROMに書き込まれたデータをテストする場合のROMテスト時間の短縮方法に於いて、複数個のROMの二つずつのROMの出力データのビット毎の比較を行う比較手段を備え、該比較手段の出力を複数個のROMに対応してそれぞれ記憶させ、該複数の記憶手段の出力データに対して、演算の順序が異なる少なくとも二つの異なる内容の演算を行い、該演算結果を期待値と比較することでROMデータを検査する。

(もっと読む)

シュミットインバータ回路及び半導体装置

【課題】チャタリング抑制の特性を維持したまま、電源電圧や温度の影響による出力周波数の変化を抑制する。

【解決手段】スイッチSWH及びSWLがオフ状態で、入力信号がVthLより大きくVDD/2未満の場合、第1インバータ12の閾値電圧はVDD/2となり、出力信号OUTはハイレベルとなる。入力信号がVDD/2〜VthHとなると、出力信号OUTが立ち下がり、制御信号CSLが立ち上がって、スイッチSWLがオンされ、閾値電圧は低電位側に変化する。入力信号がVthHを超えると、信号SLHが立ち下り、入力信号が再びVthH未満となると、信号SLHが立ち上がり、制御信号CSLが立ち下がって、スイッチSWLがオフされ、閾値電圧は再びVDD/2に変化する。入力信号がVDD/2〜VthLとなると、出力信号OUTが立ち上がり、制御信号CSHが立ち上がって、スイッチSWHがオンされ、閾値電圧は高電位側に変化する。

(もっと読む)

プログラム性能の測定方法

【課題】従来の方法では、プログラムメモリ空間にハンドラが存在しなければならず、プログラムメモリ空間の制約が厳しい組み込み系では、適用できない場合があり、また、割り込み移行時間およびハンドラでの測定用プログラムコードの処理時間が発生するため、精度が要求される実行時間の測定には不向きであった。

【解決手段】アドレス監視手段2とプログラムカウンタ4と信号発生手段3とを少なくとも備えた組み込みシステムに於けるプログラム性能の測定方法に於いて、アドレス監視手段2がプログラムカウンタ4を監視し、所定のアドレスのプログラムコードが実行された場合に、アドレス監視手段2が信号発生部4に対して、所定の表示信号パタンの出力を指示する。

(もっと読む)

PWM信号出力回路とPWM信号出力制御方法およびプログラム

【課題】複数PWM信号を自由に設定可能なPWM信号出力回路で各PWM信号の相補の使用を適正に行う。

【解決手段】クロック計数用のカウンタとデッドタイム値記憶用レジスタと、開始設定値と停止設定値が設定され且つ生成した自開始信号で立上り自停止信号で立下るPWM信号を各々出力する複数のPWM信号出力手段とを備え、各々先の立下げPWM信号を出力する前段側と次の立下げPWM信号を出力する後段側とし、後段側は自開始設定値と前段側の停止設定値との差がデッドタイム値より小さく当該停止設定値とデッドタイム値の和がカウンタ値と一致した場合に、また差がデッドタイム値以上で自開始設定値とカウンタ値とが一致した場合に開始信号を生成し、前段側は自開始設定値がデッドタイム値より小さくデッドタイム値とカウンタ値が一致すると、また自開始設定値がデッドタイム値以上で自開始設定値とカウンタ値が一致すると開始信号を生成する。

(もっと読む)

21 - 30 / 898

[ Back to top ]