ラピスセミコンダクタ株式会社により出願された特許

41 - 50 / 898

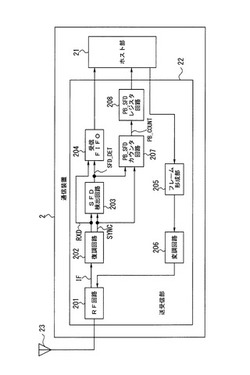

データ通信システム、プリアンプル長最適化方法、及び通信装置

【課題】 通信装置間の伝送環境に応じて最適なプリアンブル長を設定してフレームを効率よく送受信することができるデータ通信システム、プリアンプル長最適化方法、及び通信装置を提供する。

【解決手段】 第1通信装置から送信されて第2通信装置において受信されたフレーム中のプリアンブルに基づいてビット同期を検出する同期検出手段と、第2通信装置の受信フレーム中の同期検出手段によるビット同期検出位置を示す同期位置情報を生成する同期位置情報生成手段と、同期位置情報に基づいてプリアンブルの長さの最適値を算出するプリアンブル長算出手段と、その最適値に基づいた長さのプリアンブルを含むフレームの第1通信装置から第2通信装置への送信を命令する送信命令手段と、を備える。

(もっと読む)

半導体記憶装置

【課題】ヒューズセットを用いた冗長セル列の選択の簡易化を図る。

【解決手段】半導体記憶装置は、メモリセルブロック40−1,・・・と、複数の冗長セル列41−11,・・・と、冗長判定信号をそれぞれ出力する複数のアドレス判定回路50−11,・・・と、前記冗長判定信号に基づき、アドレス信号をデコードして冗長セル列41−11,・・・及びメモリセルブロック内のメモリセル列を選択する複数のデコーダ60−11,・・・とを備えている。各アドレス判定回路は、不良メモリセルの位置を示す冗長位置情報を持つヒューズ51a−1〜51a−8と、メモリセルブロックを選択するためのブロック選択情報を持つヒューズ51a−9と、を有するヒューズセット51Aを備え、前記冗長位置情報がアドレス信号と一致するか否かを判定し、この判定結果にブロック選択情報を付加した冗長判定信号を出力する。

(もっと読む)

半導体記憶装置

【課題】、半導体記憶装置自身に、適切に自半導体記憶装置に関する装置情報を記憶することができる、半導体記憶装置を提供する。

【解決手段】特定ワード線(1024番目のワード線)上のステータスレジスタ42が設けられていない領域である、8番目〜255番目のビット線と交差する領域に設けられている強誘電体メモリにより生産履歴記憶容量44を構成し、生産履歴記憶容量44に、半導体記憶装置10(半導体チップ20)の生産履歴に関する情報を記憶させている。また、生産履歴記憶容量44への記憶・参照は、主記憶容量40への記憶・参照に使用される通常のコマンドと異なる特殊なコマンドが用いられる。

(もっと読む)

半導体集積回路

【課題】遷移スキャンテストにおいて遷移故障を短時間で精度良く検出できる半導体集積回路を提供する。

【解決手段】半導体集積回路1において、高速クロック動作ブロック(高速クロックグループ)及び低速クロック動作ブロック(低速クロックグループ)という、動作周波数の異なるブロック間にスキャンチェーンを配し、半導体集積回路1の遷移スキャンテストのキャプチャ動作時において、遷移スキャン用クロック制御回路7によって低速クロックグループのスキャンFFに供給されるクロックを止めるよう構成する。これにより、低速クロックグループのスキャンFFにおける信号マスクを不要にする。

(もっと読む)

半導体メモリの製造方法及び製造装置

【課題】自動的に処理レシピを変更することにより製造歩留を向上させることができる半導体メモリの製造方法及び製造装置を提供する。

【解決手段】計算部が、第2酸化膜厚、第1酸化膜厚、ゲート電極幅、アクティブ領域幅とを含む測定値を受け取り、半導体メモリのセル部の予測電流値を算出する工程(S3)と、プロセス処理実行部が、予測電流値が基準電流値以下であると判断されたときに第1処理レシピを選択し、予測電流値が基準電流値より大きいと判断されたときに第2処理レシピを選択し、第1及び第2処理レシピのうちの選択された処理レシピに従って浮遊ゲート電極の側壁を覆うSWを形成する工程(S4,S5,S6)とを有し、第2処理レシピに従って形成されたSWの第1方向の膜厚である第2のSW膜厚が、第1処理レシピに従って形成されたSDの第1方向の膜厚である第1のSW膜厚よりも大きい。

(もっと読む)

素子モデル、素子モデル作成方法、回路検証方法、及び回路検証装置

【課題】回路検証手段によらず素子の制限特性の検証を容易に行うことができる素子モデル、素子モデル作成方法、回路検証方法、及び回路検証装置を提供する。

【解決手段】少なくとも1つの素子で構成された回路の動作を検証するためのシミュレーションで使用される前記素子をモデル化した素子モデルであって、前記素子の固有の物理特性を定義した物理特性定義部と、前記素子の固有の物理特性を用いた電気的特性であって前記シミュレーションを行う電気的特性を定義する電気的特性定義部と、前記素子の固有の物理特性に応じた電気的特性の制限を示す制限特性を定義した制限特性定義部と、前記シミュレーション中に、前記素子の固有の物理特性に応じた電気的特性が前記制限特性に違反しているか否かを検証するための処理内容を示す制限特性検証部と、を含む素子モデルを作成する。

(もっと読む)

絶縁ゲート電界効果トランジスタのシミュレーション方法、シミュレーション装置および集積回路

【課題】広いレンジのゲート長には適用可能な、絶縁ゲート電界効果トランジスタのシミュレーション方法、シミュレーション装置および当該シミュレーション方法によって設計された集積回路を提供する。

【解決手段】ボディコンタクト142を有するSOI絶縁ゲート電界効果トランジスタ10のソース電流またはドレイン電流を、ゲート−ボディオーバラップ領域160の電流を余剰のゲート幅に流れる電流として考慮に入れて求める際に、余剰のゲート幅のゲート長依存性を考慮にいれてソース電流またはドレイン電流をシミュレーションする。

(もっと読む)

発振回路

【課題】高精度発振が必要な場合には発振周波数の温度依存性を低減して高精度発振を可能とすると共に、高精度発振が不要な場合には発振回路の消費電流を低減することができる発振回路を提供する。

【解決手段】発振回路は、温度依存性が調整された出力電圧を出力するバンドギャップ回路と、第1の可変抵抗を備え、バンドギャップ回路から出力された出力電圧を第1の可変抵抗の抵抗値に応じた出力電流に変換し、変換された出力電流に基づいてバイアス電流を出力する電圧−電流変換回路と、第2の可変抵抗、容量及び比較部を備え、第2の可変抵抗の抵抗値と容量の容量値とに基づく発振周波数で発振すると共に、比較部が電圧−電流変換回路から入力されたバイアス電流の電流値に応じて動作するCR発振回路と、を備える。

(もっと読む)

フレーム受信装置、フレーム送信装置、フレーム送受信システム及びフレーム送受信方法

【課題】高精度のタイムスタンプ情報を得ることができるフレーム受信装置、フレーム送信装置、これらを含むフレーム送受信システム及びフレーム送受信方法を提供する。

【解決手段】

フレーム受信装置は、下位フレームの受信時点における受信時刻を表すタイムスタンプを生成して当該下位フレームに付加してタイムスタンプ付きフレームを生成する。更に、当該タイムスタンプ付きフレームを上位フレームに変換するとともに当該上位フレームの内容に応じて当該タイムスタンプの表す受信時刻を記憶する。フレーム送信装置は、上位フレームの内容に応じてこれにフラグを付加する。更に、当該上位フレームを下位フレームに変換するとともに当該変換対象である上位フレームに当該フラグが付加されていると判別した場合に当該判別時点における現在時刻を送信時刻として記憶する。

(もっと読む)

通信端末、中継装置及びこれらを含むパケット通信システム

【課題】通信接続要求を常時受信できる状態にありながらも、平均の消費電力を低減することができる通信端末、中継装置及びこれらを含むパケット通信システムを提供する。

【解決手段】

通信端末は、通信路を介して中継装置から供給される電源電圧の下で動作しつつ、発信元識別データを含むモード切替要求パケットを当該中継装置に送信するとともに、当該電源電圧の極性反転の検出に応じて省電力動作モードにて動作する。中継装置は、当該通信路を介して当該電源電圧を当該通信端末に供給するとともに、到来したパケットが当該モード切替要求パケットであると判別した場合に当該パケットの発信元識別データに対応する通信端末についての当該電源電圧の極性を反転させる。

(もっと読む)

41 - 50 / 898

[ Back to top ]