株式会社ルネサステクノロジにより出願された特許

1,081 - 1,090 / 4,790

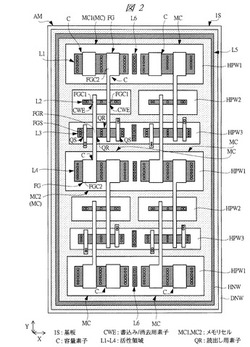

半導体装置

【課題】不揮発性メモリを備えた半導体装置のチップ面積を縮小する。

【解決手段】基板1Sの主面に形成され、隣り合って配置されたメモリセルMC1およびメモリセルMC2を含む。基板1Sの主面には、互いに電気的に分離された活性領域L1〜L4を配置する。活性領域L1にはメモリセルMC1の容量素子Cを配置し、活性領域L4にはメモリセルMC2の容量素子Cを配置する。また、活性領域L2には、メモリセルMC1の書込み/消去用素子CWEおよびメモリセルMC2の書込み/消去用素子CWEを共に配置する。さらに、活性領域L3には、メモリセルMC1の読出し用素子QRおよびメモリセルMC2の読出し用素子QRを共に配置する。

(もっと読む)

半導体装置

【課題】コンデンサとアンテナ用のコイルとの並列共振回路を非接触型インターフェイスとして持つICカードにおいて、上記コンデンサを、チップ型のセラミックコンデンサで構成するとともに、ICチップが搭載された配線基板上に半田接合する。

【解決手段】配線基板5には、上記コンデンサCと接続されたアンテナ接続端子が設けられており、配線基板5をICカードを構成するカード本体に組み込むと、配線基板5のアンテナ接続端子がカード本体に形成された上記コイルと接続される構成になっている。

(もっと読む)

携帯通信端末

【課題】比較的サイズの大きな表示パネルを有するPDAのような小型で低消費電力の携帯通信端末に好適な表示駆動方式を提供すること。

【解決手段】携帯通信端末は、表示パネル140、表示駆動制御装置100、ベースバンドプロセッサ115、アプリケーションプロセッサ116、RFユニット(図10:110)を含む。装置100の内部表示メモリ20の記憶容量は、表示パネル140の1画面分のデータ量よりも小さい。ベースバンドプロセッサ115は、装置100のレジスタ12に表示パネル140に表示される画素の階調を設定する指定ビット数を格納する。指定ビット数を小さなビット数とすることによって、表示メモリ20から静止画データを読み出して表示パネル140に静止画を表示する際に、大きなサイズの表示を可能とする一方、階調電圧生成回路36の複数のバッファ回路の一部を非活性状態に制御する。

(もっと読む)

半導体装置

【課題】素子分離にトレンチ型分離酸化膜を用いた半導体装置において分離酸化膜をCMP法で研磨する際の研磨速度の均一性を向上して表面平坦性の良好な半導体装置を得る。

【解決手段】複数の第一アクティブダミーパターン11は、分離領域10内に第一のピッチで第一の方向と第一の方向と異なる第二の方向に配置されている。複数の第二アクティブダミーパターン11は、分離領域10内に第二のピッチで第三の方向と第三の方向と異なる第四の方向に配置されている。複数の第三アクティブダミーパターン11は分離領域10内に所定の方向に第三のピッチで配置されている。第一のピッチは第二のピッチより小さく、第三のピッチは第一のピッチより小さく、第一アクティブダミーパターン11は第二アクティブダミーパターン11よりも平面積が小さく、第三アクティブダミーパターン11は第一アクティブダミーパターン11よりも平面積が小さい。

(もっと読む)

半導体素子の製造方法

【課題】半導体ウェハの大口径化に伴う素子バラツキを低減させた半導体素子の製造方法を提供する。

【解決手段】半導体ウェハ上に同一区画が碁盤目状に形成される。上記各区画には、同一の特性を持つようにされた半導体素子を形成する半導体領域を形成するために不純物がデポジションされる。上記半導体ウェハの上記デポジションされた不純物は、拡散炉により拡散される。上記拡散炉での熱処理による上記半導体ウェハの熱バラツキによるPN接合容量のバラツキは、上記不純物がデポジションされら半導体領域の面積を異なせることにより補正する。

(もっと読む)

記憶装置

【課題】先読みすべきデータを柔軟に決定することができる記憶装置を提供する。

【解決手段】不揮発性メモリ(2)、前記不揮発性メモリよりもアクセス速度の速いバッファメモリ(4)及び制御回路(5)を有し、制御回路は、外部から先読みコマンドが入力されると、前記先読みコマンドが指定する先読みデータの論理アドレスとその先読みデータを格納するバッファメモリアドレスとを対応付けた先読みデータ管理テーブルを生成し、当該コマンドが指定するデータを不揮発性メモリから読み出してバッファメモリに先読みデータとして格納し、外部から読み出しコマンドが入力されると、前記読み出しコマンドで指定される論理アドレスが先読みデータ管理テーブルで対応付けられた論理アドレスに一致するときバッファメモリから対応する先読みデータを出力する。

(もっと読む)

半導体集積回路装置

【課題】安定した内部電源電圧を発生できるように、負荷電流の変動に対して高速応答するとともに、十分な駆動電流を供給できるレギュレータ回路を提供する。

【解決手段】レギュレータ回路30aは、基準電圧VREFと内部電源電圧VINTとの差を検知増幅するプリアンプ回路32aと、プリアンプ回路32aの出力の振幅を制限するクランプ回路34aと、振幅制限されたプリアンプ回路32aの出力を増幅するメインアンプ回路36aと、メインアンプ回路36aの出力に応じて、内部電源電圧VINTを出力するドライバ回路38とを含む。内部電源電圧VINTが急激に変動しても、クランプ回路34aの効果によって、レギュレータ回路30aが発振することはない。

(もっと読む)

スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール

【課題】挿入損失を増大させることなくマルチゲートのゲート間の電位安定化が可能なスイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュールを提供すること。

【解決手段】電界効果型トランジスタを成すように、半導体基板上に形成された2個のオーミック電極39,40と、上記2個のオーミック電極の間に配置された少なくとも2個のゲート電極41,42と、隣り合うゲート電極の間に挟まれて配置された導電領域45とが備えられる。導電領域は、一端に、上記隣り合うゲート電極に挟まれている導電領域よりも幅が広い幅広部分を有し、隣り合うゲート電極の間の距離が幅広部分の幅よりも狭い。更に、幅広部分を介して2個のオーミック電極の間に直列に抵抗44,46が接続されている。

(もっと読む)

VCMドライバとPWMアンプ

【課題】低消費電力と高精度化を実現したVCMドライバ及びデットタイム歪みを補償したPWMアンプを提供する。

【解決手段】位相補償器と、位相補出力を受けて所定ビットの制御コードに変換するΔΣ変調器と、制御コードを受けてPWM信号を形成するPWM変調器と、PWM信号を受けてボイスコイルを駆動する出力回路とで往路経路を構成する。ボイスコイルの電流をセンスするセンスアンプと、センス出力を受けるADCと、ADC出力を受けるロウパスフィルタと、ロウパスフィルタ出力を受けるデシメーションフィルタとで帰還経路を構成する。デシメーションフィルタの出力を位相補償器の入力側に帰還させて一次特性のループゲインを持つ主帰還ループを構成する。デシメーションフィルタの出力を位相補償器の出力側に帰還させて、位相補償器の出力側からみて目標帯域周波数まで平坦なループゲインとする副帰還ループを構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】負電圧発生用のチャージポンプ回路の規模を低減し、又は回路自体を不要とし、チップ面積を縮小した不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルを構成するゲート電極をフローティング状態とし、隣接する他のゲート電極の電位を変化させ、この変化と容量結合比によりゲート電極の電位を減圧する。また、例えば、さらに、ゲート電極と別のゲート電極を接続してチャージシェアし、その後、別のゲート電極を隣接する他のゲート電極との容量結合により減圧することで、別のゲート電極の電位を大きく減圧させることができる。これにより、チャージポンプ回路の発生電圧レベルを低減することができる。その結果、チャージポンプ回路の規模を低減又はその回路自体を不要とすることができ、チップ面積を縮小できる。

(もっと読む)

1,081 - 1,090 / 4,790

[ Back to top ]