アドバンスト・マイクロ・ディバイシズ・インコーポレイテッドにより出願された特許

81 - 90 / 439

半導体デバイスのメタライゼーションシステムにおけるキャップ層のCMP及びエッチング停止層としての使用

【解決手段】

進歩的なメタライゼーションシステムを製造する間、敏感な誘電体材質上に形成される誘電体キャップ層が、過剰な金属を除去するためのCMPプロセスの間に部分的に維持されてよく、それにより、CMPプロセスの間に誘電体キャップ材質を実質的に完全に消耗する場合に従来の手法で必要であろうような専用のエッチング停止層を堆積させる必要性が回避され得る。従って、低減されたプロセスの複雑性及び/又は高い柔軟性が低k誘電体材質の高い完全性との組み合わせにおいて達成され得る。

(もっと読む)

同一の能動領域内に形成されるトランジスタにおいて能動領域内に局所的に埋め込み歪誘起半導体材質を設けることによる駆動電流調節

【解決手段】

共通の能動領域内に少なくとも1つの埋め込み半導体合金を設けることによって得られる異なる歪レベルに基いて、その能動領域内に形成されるプルダウントランジスタ及びパストランジスタの駆動電流能力を調節することができ、それにより能動領域の単純化された全体的な幾何学的構造を提供することができる。従って、能動領域の単純化された構造を伴う最小のチャネル長に基きスタティックRAMセルを形成することができ、プルダウン及びパストランジスタに対する駆動電流の比を調節するためにトランジスタ幅の明白な変化が従来的に用いられている洗練されたデバイスで観察され得るような顕著な歩留まり低下を回避することができる。

(もっと読む)

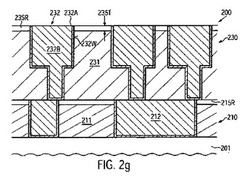

分離溝ライナを有する半導体デバイス、及び関連する製造方法

【解決手段】

半導体デバイス(300)を製造する方法がここに提供され、結果として得られる半導体デバイス(300)においては幅効果が低減されている。方法は、半導体材質(202)を有する基板(200)を提供することと、半導体材質(202)内に分離溝(212)を形成することと、その上への高k材質の形成を実質的に阻止するライナ材質(214)で分離溝(212)をライニングすることとを含む。内側を覆われた溝(216)は次いで絶縁材質(218)で充填される。その後、絶縁材質(218)の少なくとも一部分を覆い且つ半導体材質(202)の少なくとも一部分を覆うように高kゲート材質(232)の層が形成される。ライナ材質(214)は高kゲート材質(232)の層を分割し、それにより半導体材質(202)の能動領域上での酸素の泳動が防止される。

(もっと読む)

スルホールビアのための炭素ベース材質を備えた半導体デバイス

【解決手段】

半導体デバイスにおいて、デバイスの基板を通って延びるスルホールビアが炭素含有材質に基いて形成されてよく、それにより高温プロセスに対する優れた適合性がもたらされる一方で、ドープされた半導体材質等と比較して優れた電気的な性能ももたらされる。従って幾つかの例示的な実施形態では、スルホールビアは臨界的な回路要素を形成するために用いられる任意のプロセスステップに先立ち形成されてよく、それにより対応する半導体デバイスのデバイスレベルに対するスルホールビア構造の任意の干渉を実質的に回避することができる。その結果、高度に効果的な三次元集積化スキームを実現することができる。

(もっと読む)

チップ・パッケージ相互作用安定性を高めるための応力緩和ギャップを含む半導体デバイス。

【解決手段】

単一チップ区域を個々のサブ区域(1つ以上の応力緩和領域280a、280bに基く200a、200b、200c)に分割することによって、サブ区域の各々内に熱的に誘起される応力は、複雑な集積回路の動作の間に低減することができ、それにより低k誘電体材質又はULK材質を備えた複雑なメタライゼーションシステムの全体的な信頼性を高めることができる。その結果、従来の戦略と比較して、多数の積層メタライゼーション層を半導体チップ(200)の大きな横方向寸法との組み合わせにおいて用いることができる。

(もっと読む)

ダブルチャネルトランジスタを備えたSRAMセルのためのボディコンタクト

【解決手段】

スタティックRAMセル(250)を2つのダブルチャネルトランジスタ(200N、200P)及び選択トランジスタ(200S)に基いて形成することができ、ボディコンタクトがダミーゲート電極構造(205A)の形態で2つのダブルチャネルトランジスタの間に横方向に位置させられ得る一方、更なる矩形コンタクト(230)がゲート電極、ソース領域及びボディコンタクトを接続することができ、それによりトランジスタのボディ領域への伝導性パスが確立される。このように、従来のボディコンタクトと比較して、極めて空間効率的な構造を確立することができ、スタティックRAMセルにおけるビット密度を顕著に高めることができる。

(もっと読む)

特定用途向け集積回路のための電力消費の調整

【解決手段】

例えばグラフィックス処理ユニットのような特定用途向け集積回路(ASIC)における電力消費を調整するためのシステム、方法、及びコンピュータプログラム製品が提供される。当該方法においては、ASIC内に含まれるコンピュータ可読情報からASICの漏れ電流の値が受け取られる。ASICの漏れ電流の値に基いて、ASICの1つ以上の動作パラメータ、例えばASICへの供給電圧、ASICのエンジン速度、及び/又はASICを冷却するために用いられるファンのファン速度が調節される。随意的には、1つ以上の動作パラメータは、ASIC上で実行されているアプリケーションの種類に基いても調節され得る。また、ASICへの供給電圧は、ASICの温度がスレッショルドを超えた場合に遮断されてよい(随意的に)。

(もっと読む)

ホウ素閉じ込めを強化した埋め込みSi/Ge材質を有するトランジスタ

【解決手段】

シリコン/ゲルマニウム合金(255)を備えたPチャネルトランジスタのPN接合の近傍に拡散阻害種(256A)を組み込むことによって、拡散関連のPM接合の不均一性を低減することができ、それによりデバイス安定性を高め且つ総合的なトランジスタ性能を高めることに寄与する。拡散阻害種(256A)は炭素、窒素等の形態で提供されてよい。

(もっと読む)

バーチャル化可能な高度な同期機構

【解決手段】

トランザクションのメモリシステムにおけるトランザクションを実行するためのシステム及び方法が開示される。システムは、共有メモリに結合される複数のプロセッサの1つのプロセッサを含み、プロセッサは、複数のプロセッサの実行に関するアトミックなトランザクションとしての、共有メモリへの複数のメモリアクセス動作を含むコードのセクションを実行するように構成される。実施形態によると、プロセッサは、許可されていない命令の任意のセットを複数のメモリアクセス動作が含むかどうかを決定するように構成されてよく、セットは、バーチャル化されたコンピューティング環境内で自然コンピューティング環境内におけるのと異なるように動作する1つ以上の命令を含む。メモリアクセス動作が、許可されていない命令のそれである場合には、プロセッサはトランザクションを中断する。

(もっと読む)

トレンチ分離を備えたフィン型半導体デバイスを形成する方法

【解決手段】

フィンFETデバイス構造のような半導体デバイス構造(300)を製造する方法が提供される。方法は、バルク半導体材質(302)、バルク半導体材質(302)から形成される第1の伝導性フィン構造(306)、及びバルク半導体材質(302)から形成される第2の伝導性フィン構造(308)を備えている基板を提供することとによって開始する。第1の伝導性フィン構造(306)と第2の伝導性フィン構造(308)はギャップ(322)によって分離される。次いでギャップ(322)内であって且つ第1の伝導性フィン構造(306)及び第2の伝導性フィン構造(308)に隣接してスペーサ(332,334)が形成される。その後、エッチングステップが、スペーサ(332,334)をエッチングマスクとして用いてバルク半導体材質(302)をエッチングしてバルク半導体材質(302)内に分離トレンチ(336)を形成する。スペーサ(332,334)を覆い、第1の伝導性フィン構造(306)を覆い、且つ第2の伝導性フィン構造(308)を覆うように分離トレンチ(336)内に誘電体材質(340)が形成される。その後、分離トレンチ(336)内の誘電体材質(340)を保ちながら誘電体材質(340)の少なくとも一部分及びスペーサ(332,334)の少なくとも一部分がエッチングされて、第1の伝導性フィン構造の上部(342)及び第2の伝導性フィン構造(308)の上部(342)が露出させられる。これらのステップの後に、デバイスの製造は標準的な方法において完了する。

(もっと読む)

81 - 90 / 439

[ Back to top ]