アドバンスト・マイクロ・ディバイシズ・インコーポレイテッドにより出願された特許

71 - 80 / 439

傾斜型の光学的特性を有するBARCを用いるフォトリソグラフィを実行するための方法

【解決手段】

傾斜型の光学的特性を有するBARCを用いるフォトリソグラフィ方法が提供される。例示的な実施形態においては、フォトリソグラフィ方法は、パターニングされるべき材質を覆うBARCを堆積させるステップを備えており、BARCは屈折率及び吸光度を有する。BARCは、その修正のステップの後に屈折率及び吸光度の値がBARCの第1の表面での第1の値からBARCの第2の表面での第2の値まで傾斜型になるように修正される。修正のステップは堆積させるステップの後に実行される。

(もっと読む)

基板全域にわたって高められた均一性を有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

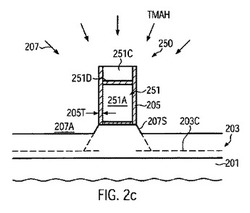

洗練された半導体デバイスにおいては、異なる結晶方位に対して異方性エッチング挙動を有し得るウエット化学的エッチングプロセスに基いてキャビティを形成することによって、チャネル領域の近くに歪誘起半導体合金を位置させることができる。1つの実施形態では、異方性エッチング挙動に加えて二酸化シリコンに関する高いエッチング選択性を呈するTMAHを用いることができ、それにより、チャネル領域からのオフセットを更に減少させる可能性を追加的に提供する一方で、全体的なプロセスばらつきの大きな原因となることのない極めて薄いエッチング停止層が可能になる。

(もっと読む)

チップ内能動的熱伝達システムを備えた半導体デバイス

【解決手段】

ペルチェ要素のような熱電要素を半導体デバイス内に設けることによって、全体的な熱管理を高めることができる。幾つかの例示的な実施形態では、温度臨界回路部分と積層チップ構造のヒートシンクの間での効率的な熱伝導経路を確立するように、対応する能動的な冷却/加熱システムが積層チップ構造内で用いられてよい。

(もっと読む)

多重プロセッサアーキテクチャ及び方法

【解決手段】

多重プロセッサアーキテクチャ及び方法の実施形態がここに開示される。実施形態は、外部ブリッジ集積回路(IC)アーキテクチャの使用に対する代替案を提供する。例えば、実施形態は、多重プロセッサが外部ブリッジICを必要とすることなしに1つの周辺インタフェーススロットを使用することができるように、周辺バスを多重化する。実施形態は既知のバスプロトコルと共に使用可能である。

(もっと読む)

チャネル領域への減少させられたオフセットを有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

非長方形形状を有していてよいキャビティに基いて歪誘起半導体合金を形成することができ、二酸化シリコン材質のような適切な保護層を設けることによって、非長方形形状は対応する高温処理の間にも維持され得る。その結果、歪誘起半導体材質の横方向のオフセットを小さくすることができる一方、キャビティエッチングプロセスの間に対応するオフセットスペーサの十分な厚みをもたらすことができるので、ゲート電極完全性を維持することができる。例えば、pチャネルトランジスタは六角形形状を伴うシリコン/ゲルマニウム合金を有することができ、それにより全体的な歪転移効率を顕著に高めることができる。

(もっと読む)

ハードマスク及び二重露光により形成される半導体デバイスのコンタクト及びビア

【解決手段】

コンタクト要素がハードマスク(233)に基いて形成されてよく、ハードマスク(233)は、第1のレジストマスク(210)に基いて及び第2のレジストマスク(211)に基いて、コンタクト要素の最終的な設計寸法を代表し得る適切な交差区域(234)を画定するようにパターニングされてよい。その結果、横方向寸法の少なくとも一方は2つのレジストマスクの各々における非臨界的寸法として選択され得るので、それほど制限的ではない制約を伴うフォトリソグラフィプロセスに基いてレジストマスクの各々を形成することができる。

(もっと読む)

分散型オーディオ及びビデオ処理

【解決手段】

ローカルネットワークを介してディスプレイデバイスと相互接続される複数のデバイスの間でオーディオ及びビデオ処理タスクを分散させる方法が開示される。1つの実施形態では、ディスプレイデバイスは、幾つかの処理タスクから解放されてこれらをローカルネットワーク上のコンピュータデバイスに課し、処理性能の向上を達成する。コンピュータデバイスは、オーディオビジュアルデータを受信し、復号化し、処理し、符号化し、そして符号化されたデータを適切なデータフォーマットでディスプレイデバイスへ送信する。コンピュータデバイスにおける処理は、ディスプレイデバイスにおいて実行されるべき任意の処理と補完的である。他の実施形態では、ディスプレイデバイスはローカルネットワーク上の複数のデバイスを利用して特定の信号処理タスクを実行する。ネットワークにおける他のデバイスは、ディスプレイによって示される処理タスクを実行し、そして処理されたデータを提示のためにディスプレイデバイスへ返送し、全体的なオーディオビジュアルデータ処理性能の向上が支援される。

(もっと読む)

高応力下にあるチャネルを有するMOSデバイスを製造するための方法

【解決手段】

シリコン含有基板を備えた半導体デバイスを形成するための方法が提供される。1つの例示的な方法は、シリコン含有基板を覆う多結晶シリコン層を堆積させることと、多結晶シリコン層をアモルファス化することと、アモルファス化された多結晶シリコン層をエッチングしてゲート電極を形成することと、ゲート電極を覆う応力誘起層を堆積させることと、シリコン含有基板を焼鈍してゲート電極を再結晶化することと、応力誘起層を除去することと、ゲート電極をエッチングマスクとして用いて基板内へ凹部をエッチングすることと、凹部内に不純物ドープのシリコン含有領域をエピタキシャル成長させることとを備えている。

(もっと読む)

疎及び密予測を伴うハイブリッド分岐予測デバイス

【解決手段】

マイクロプロセッサにおける分岐予測のためのシステム及び方法。ハイブリッドデバイスは、命令キャッシュの各エントリ内の通常のより小さい数より多くない分岐に対して疎キャッシュ内に分岐予測情報をストアする。iキャッシュラインが追加的な分岐を備えているあまり一般的でない場合に対しては、デバイスは、対応する分岐予測情報を密キャッシュ内にストアする。疎キャッシュの各エントリは、対応する命令キャッシュラインが追加的な分岐命令を含んでいるか否かを表示するビットベクタをストアする。この表示はまた、記憶のための密キャッシュ内のエントリを選択するために用いられてよい。第2の疎キャッシュは、第1の疎キャッシュから退去させられた全てのエントリをストアする。

(もっと読む)

アクティブ層の厚み減少を伴う歪トランジスタを形成するための構造歪を与えられた基板

【解決手段】

歪を与えられたSOI半導体層において、典型的には溝分離構造のパターニングの間に生じ得る応力緩和は、アクティブ領域の適切に減少させられた目標高さを選択することによって低減することができ、それにより、顕著な量の初期歪成分を未だに含むであろう減少させられた高さのアクティブ領域上へのトランジスタ要素の形成が可能になる。減少させられた高さのアクティブ領域は、完全に減損した電界効果トランジスタを形成するために有利に用いることができる。

(もっと読む)

71 - 80 / 439

[ Back to top ]