アイメックにより出願された特許

291 - 300 / 302

ウェハ相互接続用三次元ウェハのための深いビアエアギャップの形成

【課題】サーマルバジェットに関する問題を解決し、三次元の積層半導体素子を作成する方法を提供する。

【解決手段】基板内にホールをパターニングするステップと、このホールに部分的に犠牲材料を充填するステップと、このホールの充填されていない部分の側壁にスペーサを形成し開口を狭めるステップと、犠牲材料の残留物をこの狭められた開口から除去するステップと、最後にスペーサ上に共形層を堆積することでエアギャップの開口を密封するステップとから構成される、半導体基板内に深いエアギャップを形成する方法が開示される。深いビアエアギャップを形成する方法はウェハ同士の垂直積層を作成するのに用いられる。従来のFEOLおよびBEOL処理の完了後、深いビアエアギャップが開口されるようにウェハの裏面が薄くされ、導電性材料がこのビア開口内に堆積され、導電性材料が充填されたスルーウェハもしくは深いビアが作成される。

(もっと読む)

深溝エアギャップの形成とその関連応用

【課題】 バイポーラCMOSデバイスにおける深溝の絶縁分離構造として使用できるエアギャップを形成する方法を提供する。

【解決手段】 エアギャップの形成方法は、基板内の穴をパターン処理し、上記穴を例えばポリシリコンなどの犠牲材料で充填し、穴の未充填部の側壁に例えばTEOSスペーサを形成して開口を狭め、犠牲材料の残部を例えば等方性エッチングにより上記狭められた開口を通して除去し、最後に、スペーサの上方に準拠層(TEOS)を形成することにより、エアギャップの開口を封止する工程を有する。

(もっと読む)

不活性化された半導体基板の作成方法

【課題】 更なるIC処理に関してシリコン以外の半導体材料を含む半導体基板を不活性化するための方法を提供する。

【解決手段】 不活性化された半導体基板を作成する方法であって、シリコン以外の半導体材料を含むか、または、シリコン以外の半導体材料より成る単結晶基板の表面を提供する工程と、シリコン層が基板表面の該当部分に実質的に格子整合するように、シリコン層を基板表面に形成する工程とを備える。

(もっと読む)

半導体基板のキャリア濃度レベルと電気接合深さを独立して引き出す方法および装置

本発明は、1回の方法で、互いに独立して、半導体基板のキャリア濃度レベルと接合深さとを、非破壊の方法で特定するための方法および装置を提供する。  (もっと読む)

(もっと読む)

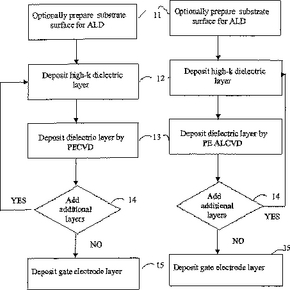

誘電体スタックの形成方法

本発明は、集積回路の中に誘電体スタックを形成する方法を提供し、(i)半導体基板上に高−k誘電体層を形成するステップと、(ii)高−k誘電体層を有する半導体基板を、プラズマ化学気相成長方法(PECVD)またはプラズマ原子層化学気相成長法(PEALCVD)において、窒素含有気相反応物およびケイ素含有気相反応物で処理するステップとを含む。さらに、本発明は、(i)少なくとも高―k材料を含む高―k誘電体層と、(ii)少なくともケイ素および窒素を含む誘電体層と、(iii)前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含む集積回路中の誘電体スタックを提供し、前記中間層は前記高―k材料、ケイ素および窒素を含む。  (もっと読む)

(もっと読む)

過渡的なキャビテーションを制御する方法及び装置

【課題】 巨大な音エネルギーだけでは気泡発生が効率的でない。

【解決手段】 この発明は過渡的なキャビテーションを生成するための方法に関し、液体中にさまざまな気泡サイズを持っている気泡を生成するステップと、音場を生成するステップと、および液体を音場にさらすステップとを備え、気泡サイズの範囲、および/または、音場の特性が互いにそれらを調整するように選択され、それにより、選択された範囲の気泡サイズにおいて過渡的なキャビテーションを制御することを特徴とする。この発明はこの方法を実行するのに適した装置にも関する。

(もっと読む)

タングステン系のバリアメタルと一体化された銅を化学機械研磨するためのスラリー組成物及び方法

【課題】商業的に入手可能な研磨スラリーの欠陥を解消し、電解腐食を防止しつつ、一体化されたW含有バリアを備えたCu構造物を研磨することを可能にするスラリー組成物を提供する。

【解決手段】タングステンを含んでいるバリア層と一体化された銅を研磨するためのスラリー組成物と、CMP法におけるその使用方法とに関するものであり、また、タングステンを含有しているバリア層と一体化された銅を研磨するための方法に関するものである。この方法は、研磨粒子と、タングステンを含有しているバリアメタルの電解腐食を防止する銅エッチング液であるHNO3などの無機酸と、銅の腐食を十分に防止するための少なくとも1つの有機化合物とを含んでいるスラリー(水溶液)を用いて行われる。

(もっと読む)

光リソグラフィの迷光の影響を減らす方法、その方法によって得られたデバイスおよびその方法に使用されるマスク

【課題】 光リソグラフィの間に、特性の大きさ上に伝達される光の拡散の影響を減らす方法。

【解決手段】 本方法は少なくとも2回の照射ステップを含む。第1の照射ステップの間、レジストが、元のマスク(100)すなわち層の中に得られるパターンを実質的に含む元のマスクで露光される。その後で、露光されたレジスト(140)を現像せずに、少なくとも1回の露光の照射ステップが実施され、それによってレジスト(140)が、少なくとも部分的に元のマスク(100)の逆である第2のマスクで露光される。第2の照射ステップの露光は、第1の照射ステップと比較して、デフォーカスする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】HEMT性能を向上させる。

【解決手段】

本発明は、ヘテロ構造上で、若干のHEMTトランジスタを製造する方法と同様に、MOCVDを用いてSiN層をいささかも除去することなく、表面に接点を蒸着させることにより、構造の冷却および反応器からの試料の取り出しに先立ち、高温で成長が起こる反応器内で、最上部AlGaN層上の表面を薄いSiN層で覆うことにより、より高性能(出力)を伴い、有機金属気相成長法により成長させられた、HEMT、MOSHFET、MISHFET素子、またはMESFET素子のような、III族−N電界効果素子を製造するための新規な方法を解説している。本発明は素子も解説している。

(もっと読む)

液浸リソグラフィの方法および装置

【課題】 本発明は、一方では液による基板の不十分な液浸のために気泡が形成し、他方では液が漏出したり、液体が蒸発するという二律背反性に許容範囲を新たに提供することである。さらに、本発明は乾燥による残留物形成のリスクを軽減することである。

【解決手段】 液浸リソグラフィの方法および装置が説明されている。この方法は、液浸露光ヘッドアセンブリの下の半導体基板の位置決めをするステップ、基板と液浸露光ヘッドアセンブリとの間に浸液を提供するステップおよび浸液と基板との接触領域の境界線に沿って、界面活性のガス状の物質を供給するステップを含む。浸液は基板の少なくとも一領域に接する。少なくとも部分的に浸液と混ぜられたとき、浸液よりも低い表面張力をもつ混合物が形成されるように、界面活性のガス状の物質が選択されるので、境界線から接触領域へ浸液を引っ張る表面張力勾配をつくる。

(もっと読む)

291 - 300 / 302

[ Back to top ]