アイメックにより出願された特許

221 - 230 / 302

主電極を含むドープされた金属を含む半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

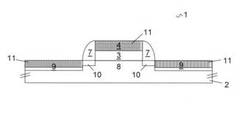

【解決手段】半導体装置は、主電極(4)と主電極(4)に接触した誘電体(3)を含み、主電極(4)は、所定の仕事関数を有する材料と、主電極(4)の材料の仕事関数を予め決められた値に向かって変調する仕事関数変調元素(6)とを含み、更に、主電極(4)は、仕事関数変調元素(6)が誘電体(3)に向かっておよび/または誘電体(3)中に拡散するのを防止する拡散防止ドーパント元素(5)を含む。

(もっと読む)

AlGaN/GaNHEMTの表面処理およびパッシベーション

好適に具体例では、ゲートリークと散乱を低減した、薄いその場SiN層により覆われたIII族窒化物電界効果デバイスが提供される。これは、ゲート堆積の前と、第2パッシベーション層の堆積前の、その場SiNの洗浄と組み合わせて、その場SiN層の上に第2のパッシベーション層を導入して得られる。  (もっと読む)

(もっと読む)

YBがドープされたポリシリコンゲートのドライエッチング方法

【課題】本発明は、従来の反応性イオンエッチングの間、揮発性の化合物を生成しない元素、例えばイットリビウム(Yb)が注入されたポリシリコンゲートをエッチングすることを目的とする。

【解決手段】本発明は、従来の反応性イオンエッチングを用いて、揮発性の化合物を形成しない元素を含むスタックをパターニングする方法に関する。より詳細には、上記元素はイットリビウム(Yb)等のランタニド元素であり、上記パターニングは、例えばイットリビウム等のランタニド元素がドープされたシリコン及び/又はゲルマニウム含有構造(例えばゲート)である(例えばYbドープゲート)。当該シリコン及び/又はゲルマニウム含有構造がゲート電極である場合、ゲート電極の仕事関数をモデリングするため、上記シリコン及び/又はゲルマニウムにランタニド元素(例えばYb)をドープする。

(もっと読む)

マイクロマシンデバイスの製造方法

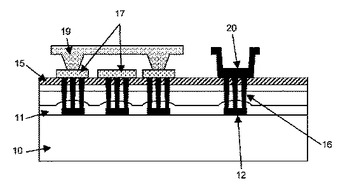

本発明は、電気回路を含む基板(10)の上に、少なくとも1つのマイクロマシン構造を含むマイクロマシンデバイスを、下方の電気回路に影響を与えることなく作製する方法を提供する。この方法は、電気回路を含む基板(10)の上に、保護層(15)を形成する工程と、少なくとも1つのマイクロマシン構造を形成するための複数のパターニングされた層を保護層(15)の上に形成する工程であって、複数のパターニングされた層は、少なくとも1つの犠牲層(18)を含む工程と、その後に、犠牲層(18)の少なくとも一部を除去して、少なくとも1つのマイクロマシン構造を開放する工程とを含む。この方法は、更に、保護層(15)を形成する前に、マイクロマシンデバイスの製造中に使用される最高温度より高い温度で基板(10)をアニールする工程を含み、アニールは、その後の製造工程中に、保護層(15)の下での気体の形成を防止する。本発明は、また、本発明の具体例にかかる方法で得られたマイクロマシンデバイスを提供する。  (もっと読む)

(もっと読む)

半導体デバイス層からの不純物の除去

本発明は、半導体デバイス(1)の製造中に、少なくとも一つの半導体デバイス層(4)から該半導体デバイス層(4)を用いて不純物を除去する方法を提供し、上記少なくとも一つの半導体デバイス層(4)は、化合物半導体材料及び/又はゲルマニウムを備え、少なくとも一つの半導体デバイス層(4)を準備した後、半導体デバイス(1)の製造中に実行される各加熱工程は、900℃以下の温度で、5分以下の時間により決定される低サーマルバジェットを有する。上記方法は、半導体デバイス層(4)よりも不純物に関して高い溶解度を有するゲルマニウム・ゲッタリング層(3)を設けることを備え、ゲルマニウム・ゲッタリング層(3)は、少なくとも一つの半導体デバイス層(4)に直接又は間接に接触して少なくとも部分的に設けられ、これにより、不純物は、少なくとも一つの半導体デバイス層(4)からゲルマニウム・ゲッタリング層(3)へ拡散することができる。本発明は、また、発明の実施態様による不純物の除去方法を用いて半導体デバイスを形成する方法を提供し、及びそれにて得られる半導体デバイスを提供する。  (もっと読む)

(もっと読む)

ヘテロ構造を有する細長い単結晶ナノ構造に基づくトンネル効果トランジスタ

【課題】トンネル電界効果トランジスタ(TFET)は、金属酸化物電界効果トランジスタ(MOSFET)の後継者と考えられるが、シリコンベースのTFETは一般に低いオン電圧、トンネルバリアの大きな抵抗による欠点が問題となる。より高いオン電流を得るために、異なった半導体材料(例えばゲルマニウム(Ge))からなるヘテロ構造を備えた細長い単結晶ナノ構造ベースのTFETが用いられる。

【解決手段】TFETのソース(又は代わりにドレイン)領域として機能する、異なった半導体材料からなる細長い単結晶ナノ構造を導入する。ヘテロ部分の導入は、シリコンとゲルマニウムの間の格子不整合が高い欠陥界面とならないように行われる。従来のMOSFETに匹敵する、静的電力の低減と同様に動的電力の低減が行われる。細長い単結晶ナノ構造のSi/GeTFETによる超高密度オンチップトランジスタを用いた、多層の論理が期待される。

(もっと読む)

半導体装置の接合形成方法およびそれにより作製された半導体装置

【課題】半導体装置の所望のソース/ドレイン接合深さの近傍にある、エンドオブレンジ(EOR)領域の存在の、負の影響を低減する。

【解決手段】装置とその装置の製造方法が記載され、それにより、装置がエンドオブレンジ欠陥から離れた浅い接合深さを有する。方法は、シリコンのような結晶半導体中に、第1深さまで、アモルファス領域を形成する工程と、これに続いて、例えば炭素のような置換型元素を、第1深さより浅い深さまで注入する工程とを含む。続いて領域は例えばリンやボロンのような適当なドーパントでドープされ、熱処理工程によりアモルファス領域が再結晶化される。

(もっと読む)

レジストの最適化によるウオータマーク欠陥の低減

【課題】液浸リソグラフィー処理用の良好な方法、及び良好な液浸リソグラフィー処理を得るための適切な材料を提供する。

【解決手段】リソグラフィー処理方法が記載されている。該方法は、所定のレジスト特性を有するレジスト材料250を取得し、リソグラフィー処理されたデバイスにレジスト層4を設けるため上記レジスト材料を使用し、及び、得るべき所定パターンによって上記レジスト層を照明することを備える。これにより得られたレジスト材料250は、上記リソグラフィー処理されたデバイスのウオータマーク欠陥を低減するように、調整された光酸発生剤成分254の濃度、及び/又は調整されたクェンチャー成分256の濃度、及び/又は調整された酸移動性を備える。本発明は、また、対応のレジスト材料250、レジスト材料群、そのような材料の使用、及びリソグラフィー処理の組立方法に関する。

(もっと読む)

レジスト層を基板から除去する方法

【課題】実施が容易で、デバイス性能に影響を与えずに、レジスト層を基板から除去する方法を提供する。

【解決手段】基板に接触するバルクレジストと、レジスト層の外表面に存在するレジスト外皮とを備えたレジスト層を、基板から除去する方法であって、基板に接触するレジスト層に、バルクレジストについて可溶でレジスト外皮について不溶である液体有機溶媒を少なくとも局所的に供給するステップと、メガソニックエネルギーを有機溶媒に供給して、レジスト外皮を解体し、バルクレジストを有機溶媒中に溶解させる有機溶媒キャビテーションを生成することによって、レジスト層を基板から剥がすステップとを含む。

(もっと読む)

リソグラフ要素の汚染測定方法およびシステム

【課題】リソグラフ要素の汚染を特徴付けるための良好な方法およびシステムを提供する。

【解決手段】リソグラフ要素の汚染を測定する方法は、第1リソグラフ要素を処理チャンバ内に設けるステップと、第2リソグラフ要素を処理チャンバ内に設けるステップと、第1リソグラフ要素の一部を被覆して、第1リソグラフ要素の被覆部分である参照領域を第1リソグラフ要素に設けるステップと、処理チャンバ内に汚染物質を供給するステップと、露光ビームを、第1リソグラフ要素のテスト領域および第2リソグラフ要素に向けて、少なくとも1つのリソグラフ要素が汚染物質によって汚染されるようにするステップと、処理チャンバ内で、少なくとも1つの汚染されたリソグラフ要素の汚染レベルを測定するステップとを含む。

(もっと読む)

221 - 230 / 302

[ Back to top ]