アイメックにより出願された特許

121 - 130 / 302

MEMSデバイスの検査構造及び方法

【課題】半導体装置においてアンダーエッチングを測定する。

【解決手段】構造40a〜40e中に犠牲層41c〜41eの存在を判断する方法で、該方法は、平面にてなる主面を有する基板に配置された少なくとも一つの構造40a〜40eを設け、ここで上記少なくとも一つの構造は、少なくとも一つの側部で固定され、所定の大きさの力、例えば機械的力が当該構造に作用し、基板に垂直な部品を有し、かつ、基板の上記平面に垂直な上記少なくとも一つの構造の歪みを判断し、かつ、上記少なくとも一つの構造の歪みを、上記基板と上記構造との間の犠牲層の存在に関連づけることを備える。

(もっと読む)

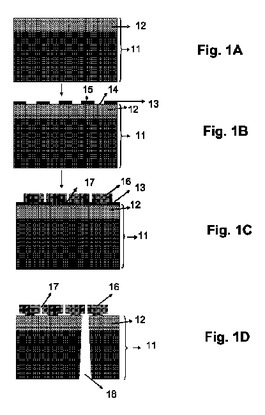

集積回路用相互接続構造の製造方法

【課題】化学機械研磨(CMP)を用いて過剰なバリアと導電材料を除去して、これにより堆積における不均一性を補償するより広いプロセスウインドウを形成する半導体デバイスの製造方法を提供する。

【解決手段】基板1の表面上に、誘電体材料のトップ層2を堆積する工程と、第1開口部7をエッチングし、第1導電性材料8を用いて第1開口部を充填し、第1CMP工程を行って、第1導電性構造3を形成する工程と、1つの第2開口部13をエッチングし、第2導電性材料10を用いて第2開口部を充填し、第2CMP工程を行って、第2導電性構造4を形成する工程と、を含み、第1開口部をエッチングし充填する工程の前に、誘電体トップ層の上に共通のCMPストップ層5を堆積して、第1開口部の充填後のCMPプロセスと第2開口部の充填後のCMPプロセスとを停止するために使用する工程とを含む。

(もっと読む)

抵抗スイッチングメモリデバイスの製造方法およびそのデバイス

【課題】CMOS互換の処理フローにおいて抵抗スイッチング材料の集積化を容易にする抵抗スイッチングメモリデバイスの製造方法を提供する。

【解決手段】抵抗スイッチングメモリデバイス(115)の製造方法は、電気コンタクト(101)を含む基板(100)を用意すること、電気コンタクト(101)を露出させる溝を含む絶縁層(102)を基板(100)上に設けること、溝の中に、少なくとも抵抗メモリデバイス(115)の下部電極(103b)および抵抗スイッチング素子(140)を設けること(186)を含む。該方法は、上部電極(105)を、抵抗スイッチング素子(140)と接触するように少なくとも溝の上または中に設けることをさらに含む。本発明はまた、対応した抵抗スイッチングメモリデバイス(115)を提供する。

(もっと読む)

伝送線路パルス試験システムの較正方法

【課題】伝送線路パルス試験システムを較正する方法。

【解決手段】TLP試験システムの過渡的な挙動を較正するための較正方法。TLP試験システムは、TLP発生器と、プローブ針と、公称でインピーダンス整合のとれた伝送線路と、伝送線路とTLP発生器との間に接続され、生成されたパルスの結果としての電圧及び電流の波形を同時に取得することにより、被試験素子の過渡的な挙動を検出する計測器と、を有する。較正方法は、(a)TLP試験システムを開路に適用し、第1の電圧及び電流の波形を取得するステップと、(b)TLP試験システムを既知の有限インピーダンスと既知の過渡応答を含む較正要素に適用し、第2の電圧及び電流の波形を取得するステップと、(c)取得した第1及び第2の電圧及び電流の波形を周波数領域に変換するステップと、(d)変換された第1及び第2の電圧及び電流の波形に基づいて、TLP試験システムの過渡的な挙動についての較正データを決定するステップと、を含む。

(もっと読む)

有機電子デバイスに使用する有機層の結晶性ナノファイバ含有率を制御する方法

本発明は、第1の態様において、有機電子デバイス中の活性層として使用するためのナノファイバ含有層を製造する方法に関する。該方法は、以下のステップを含む。a)最初に、ナノファイバ形成ポリマーを、温度T1の溶媒中で加熱するステップ。b)次に、前記溶液を40℃/h未満の速度で、温度T2まで冷却し、前記ナノファイバ形成ポリマーからなる結晶性ナノファイバを備える分散系を作成するステップ。c)次に、前記分散系の温度をT2より高くT1より低い温度T3まで温度を上げるステップ。d)そして次に、前記温度T3で、分散系を基板上にコーティングし、前記有機電子デバイスとして使用するための層を形成するステップ。ステップ(d)の前に、溶液または分散系に電子受容体を付加するステップを実施する。  (もっと読む)

(もっと読む)

物体の表面形状を決定するための方法および装置

物体(301)の静止表面(305)の表面形状(topography)を決定するための方法は、(a)物体(301)の静止表面(305)における領域(301a)を選択するステップと、(b)入射単色電磁波(302)を領域(301a)に向けるとともに、表面(305)および入射単色電磁波(302)を互いに相対移動させるステップであって、入射単色電磁波(302)は、周波数f0、振幅A0および伝搬方向によって特徴付けられ、移動方向(304)は、入射単色電磁波(302)の伝搬方向に対して実質的に平行でなく、表面(305)は、入射単色電磁波(302)を反射し、反射単色電磁波(303)を発生し、移動(304)は、移動周波数(F)および移動振幅(A)によって特徴付けられるようにしたステップと、(c)移動(304)の際、領域(301a)から反射した単色電磁波(303)の特性を決定するステップと、(d)入射単色電磁波(302)の特性、例えば、周波数f0および反射単色電磁波(303)の特性、例えば、周波数frを解析して、物体(301)の領域(301a)の表面形状に関する情報を取得するステップとを含む。対応するシステムも提供される。  (もっと読む)

(もっと読む)

双方向ESDパワークランプ

【課題】 エリアの消費が少ない双方向ESDパワークランプを提供する。

【解決手段】 本発明は、第1のノードと第2のノードとの間に接続された導電性経路と、導電性経路をトリガすることができるトリガノードとを有する半導体構造(大きいNFET、大きいPFET)を備える双方向ESDパワークランプに関する。ESD過渡検出回路は、第1のノードと第2のノードとの間に接続され、かつトリガノードに接続され、かつ第1のノードでの第1のESD過渡の発生を検出する第1の部分(10乃至17)を備える。半導体構造は、絶縁体基板上に提供されて、基板を介した上記第1のノードと上記第2のノードとの間の寄生導電性経路が回避される。ESD過渡検出回路はさらに、第2のノードでの第2のESD過渡の発生を検出する第2の部分(M1,M2)を備える。

(もっと読む)

層を貫通するナノ構造を形成する方法

デバイスは、基板、その上に存在する層、および前記層を貫通するナノ構造を備え、ナノ構造は、分析される分子が通過可能なナノスケールの通路を規定し、ナノ構造は断面図において、実質的に三角形状を有するようにした。この形状は、ナノ構造の傾斜側壁を規定する結晶ファセットを有するエピタキシャル層の成長によって特に達成する。それは、特に表面プラズモン増強透過分光を用いた、分子構造の光学的特性評価のための使用に極めて好適である。  (もっと読む)

(もっと読む)

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

有機デバイスの電気コンタクトを形成するための溶液処理方法

本発明は、有機半導体層の上に、金属を含む電気コンタクト層を形成する方法に関し、この方法は、(a)有機半導体層の上に電荷収集バリア層を提供する工程と、(b)電荷収集バリア層の上に金属のための前駆体を含む液体合成物を提供する工程と、(c)シンタリング工程を行う工程とを含み、電荷収集バリア層は、液体合成物の成分に対して実質的に不浸透性である。  (もっと読む)

(もっと読む)

121 - 130 / 302

[ Back to top ]