アイメックにより出願された特許

111 - 120 / 302

磁性層のパターニングと接続

本発明の具体例にかかる方法は、磁性層(41)と、下部導電性電極(43)と、その反対側で磁性層サブスタックを電気的に接続する上部導電性電極(44)とを含む磁性層サブスタックを含む磁気スタックを形成する工程と、磁気スタックの上に犠牲柱(46)を形成する工程であって、犠牲柱(46)は上に横たわる第2の犠牲材料(45)に対するアンダーカットと、磁気スタックに向かって断面寸法が大きくなる傾斜フットを有する工程と、犠牲柱を磁気スタックのパターニングのために使用する工程と、犠牲柱(46)の周囲に絶縁層(70)を堆積する工程と、犠牲柱を選択的に除去し、これによりパターニングされた磁気スタックに向かってコンタクトホール(80)を形成する工程と、コンタクトホールを電気的な導電性材料(81)で埋める工程とを含む。  (もっと読む)

(もっと読む)

MOSトランジスタ

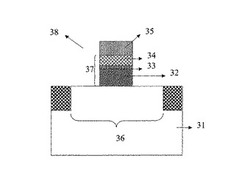

【課題】MOSトランジスタを作成する。

【解決手段】MOSトランジスタであって、ゲート電極と、ゲート電極下地の頂部表面を有するチャンネル領域と、ゲート電極とチャンネル領域の頂部表面の間に挿入された誘電体スタックとを含み、前記誘電体スタックが、少なくとも高―k材料を含む高―k誘電体層と、少なくともケイ素および窒素を含む誘電体層と、前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含み、該中間層が、少なくとも前記高―k材料、ケイ素および窒素を含み、前記ゲート電極がポリシリコンまたはポリシリコンゲルマニウムから作製される。

(もっと読む)

導波路集積型光検出器

導波路集積型光検出器(100)を記載している。導波路集積型光検出器は、プラズモンサポート材料から成る第1層(110)を備え、第1層(110)は、第1放射線を導波路と結合させるために第1層を貫通する入力スリット(112)を有する。光検出器(100)はまた、プラズモンサポート材料からなり、第1層(110)に面し、第1層(110)から第1方向に第1距離を隔てた第2層(120)を有する。第2層(120)は、第2層(120)を貫通し、入力スリット(112)から第1方向と異なる第2方向に沿って第2距離隔てた出力スリット(122)を有する。光検出システム(100)はまた、第1層(110)と第2層(120)との間に配置した誘電体層(130)、および出力スリット(122)に近接する、出力スリット(122)を通って出射する結合した放射線を検出するための、検出器(140)とを備える。  (もっと読む)

(もっと読む)

半導体領域の接合深さを測定する方法および装置

【課題】光変調光反射測定技術を用いて、基板の半導体接合の深さの値を測定する方法。

【解決手段】半導体接合を含む少なくとも第1領域を有する基板を得る工程と、参照領域を得る工程と、少なくとも1回、以下のシーケンス、光変調光反射率測定のための測定パラメータのセットを選択する工程110、選択されたパラメータのセットを用いて、少なくとも第1領域の上で、半導体接合を有する基板を表す第1光信号を測定する工程120、選択されたパラメータのセットを用いて、参照領域の上で、第2光信号を測定する工程130、および第2光信号に対する第1光信号の比を測定し(140)、この後に、この比から、半導体接合の深さを導き出す工程150を行う工程とを含む。

(もっと読む)

ダメージを低減した物理力アシスト洗浄方法

【課題】パターニングされた基板(パターン基板)の物理力アシスト洗浄で誘起されるダメージを低減する。

【解決手段】洗浄プロセスは、a)少なくとも1つのパターン表面を有する基板を準備する工程と、b)洗浄液3をパターン表面に供給する工程と、c)パターン表面に接触した洗浄液に物理力を供給し、これにより物理力が洗浄液中に気泡を形成する工程と、を含み、物理力を供給する前に、添加剤が表面に供給され、所定の時間、添加剤は表面に接触するように保持され、添加剤と時間は、洗浄液により表面の実質的に完全な濡れが達成されるように選択する。

(もっと読む)

プラズマテクスチャ方法

本発明は、基板の表面をテクスチャするためのドライエッチング方法に関し、この方法は以下の工程:a)基板の表面上で第1ドライエッチング工程を行い、これにより突起部と溝部とを有する表面テクスチャを形成する工程であって、第1ドライエッチング工程は、フッ素(F)ラジカルと酸素(O)ラジカルとを含むプラズマ中で基板の表面をエッチングする工程を含み、プラズマは過剰の酸素(O)ラジカルを含む工程、および、b)表面テクスチャ上で第2ドライエッチング工程を行い、これにより表面テクスチャを平坦化する工程であって、第2ドライエッチング工程は、フッ素(F)ラジカルを含むプラズマ中で、工程a)で得られた表面テクスチャを、化学等方性エッチングする工程を含み、これにより突起部が溝部より実質的に速くエッチングされる工程、を含む。  (もっと読む)

(もっと読む)

接合の作製方法

【課題】バイポーラトランジスタのエミッタ−ベース界面において、ドーパント濃度プロファイルを制御する方法を提供する。

【解決手段】第1濃度を有する第1ドーパントを含む第1半導体材料を形成する工程と、その上に、第2濃度を有し、これにより接合を形成する、第2ドーパントを含む第2半導体材料を形成する工程と、第2半導体材料を形成する前に、原子層エピタキシまたは気相ドーピングにより、第1半導体材料の上に、第2ドーパントを形成するのに適した、単分子層の少なくとも一部分の前駆体を堆積し、これにより接合における第2ドーパントの第2濃度を増加させる工程と、を含む(またはこれらの工程からなる)。

(もっと読む)

無線通信システムにおけるアナログビームフォーミングのための方法及びシステム

本発明は、無線通信システムにおけるアナログビームフォーミング方法に関し、前記システムは複数の送信アンテナ及び複数の受信アンテナを有する。当該方法は、前記複数のアンテナのうちの1つの送信アンテナと1つの受信アンテナとの間に形成された通信チャンネルを表す情報を決定し、前記送信ビームフォーミング係数及び前記受信ビームフォーミング係数とを結合して表す係数セットを定義し、前記情報及び前記係数セットを使用してビームフォーミングコスト関数を決定し、前記ビームフォーミングコスト関数を利用することにより、最適化された係数セットを決定し、前記最適化された係数セットを最適化された送信ビームフォーミング係数と最適化された受信ビームフォーミング係数とに分離することにより、送信ビームフォーミング係数及び受信ビームフォーミング係数を決定するステップを備える。  (もっと読む)

(もっと読む)

MEMSデバイスの検査構造及び方法

【課題】半導体装置においてアンダーエッチングを測定する。

【解決手段】構造40a〜40e中に犠牲層41c〜41eの存在を判断する方法で、該方法は、平面にてなる主面を有する基板に配置された少なくとも一つの構造40a〜40eを設け、ここで上記少なくとも一つの構造は、少なくとも一つの側部で固定され、所定の大きさの力、例えば機械的力が当該構造に作用し、基板に垂直な部品を有し、かつ、基板の上記平面に垂直な上記少なくとも一つの構造の歪みを判断し、かつ、上記少なくとも一つの構造の歪みを、上記基板と上記構造との間の犠牲層の存在に関連づけることを備える。

(もっと読む)

基板上に単結晶半導体層を作製する方法

【課題】基板上に高品質の単結晶半導体層を形成する。

【解決手段】基板上に単結晶の半導体材料の層を形成する方法に関し、この方法は、基板1を準備する工程と、基板上に少なくとも1つの半導体材料の単分子層2を含むテンプレートをエピタキシャル成長する工程と、テンプレート上に半導体材料のアモルファス層3を堆積する工程と、熱処理またはレーザアニールを行い、半導体材料のアモルファス層を、半導体材料の単結晶層に完全に変える工程とを含む。

(もっと読む)

111 - 120 / 302

[ Back to top ]