アイメックにより出願された特許

131 - 140 / 302

非シリコンチャネルMOSデバイス中のフェルミレベルピンニングの低減方法

【課題】金属酸化物半導体(MOS)デバイス中の、GeやIII−V化合物(例えばGaAsまたはInGaAs)のような高移動度半導体化合物チャネル中の、フェルミレベルピンニング(FLP)を低減(回避)する方法の提供。

【解決手段】半導体化合物11上のゲート誘電体19上にゲート電極20を形成し、水素アニール21を実施する。水素はゲート電極のPtやPdのような貴金属による触媒作用により原子状水素を形成しアニールを行い半導体化合物11とゲート誘電体19との界面を界面をパッシベートし、更には欠陥を回復する。

(もっと読む)

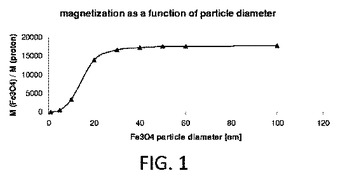

単磁区ナノ粒子の磁気共鳴イメージング

単磁区粒子を含む物体に関する情報を収集するための方法およびシステムが記載される。こうした単磁区粒子は、約5nm〜80nmの範囲の直径を有する。情報を収集する方法は、物体に印加される約0.1テスラ未満の静磁場の発生と、単磁区粒子の電子常磁性共鳴を生じさせる周波数で、パルスまたは連続波のRFエネルギーの発生とを含む。該方法は、単磁区粒子の電子常磁性共鳴を物体の画像の形態で検出することを含む。代替として、単磁区粒子は、所定の直径および所定の飽和磁化を有してもよく、印加された磁場は、単磁区粒子が飽和磁化の少なくとも約10%、好ましくはそれ以上の磁化に到達するようにしてもよい。他の実施形態では、本発明の原理は、物体中のタグを検出し、タグを活性化するために用いられる。  (もっと読む)

(もっと読む)

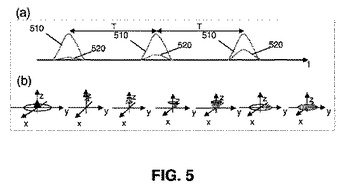

パルスEPR検出

パルス電子磁気共鳴を実行する方法およびシステムが開示される。該方法は、プローブを備える物体に印加するための励起パルス列を発生することと、励起パルス列に誘導されるエコー応答をプローブから検出することとを含む。  (もっと読む)

(もっと読む)

硬化フォトレジストを半導体基板から除去する方法

【課題】下地となる低誘電率材料にダメージを与えることなく、硬化したフォトレジストを除去する。

【解決手段】硬化したフォトレジストを、低誘電率材料を含む基板から除去し、低誘電率材料の特性を保存する方法を提供する。a)硬化したフォトレジストおよび少なくとも部分的に露出した低誘電率材料を含む基板を用意する。b)硬化したフォトレジストを、真空または不活性雰囲気で200nm〜300nmの波長を有するUV放射で露光することによって、硬化したフォトレジスト中にC=C二重結合を形成する。c)硬化したフォトレジストを、オゾン(O3)またはオゾン(O3)と酸素(O2)の混合物と反応させることによって、b)で形成されたC=C二重結合を破壊し、これにより硬化フォトレジストを断片化する。d)クリーニング化学薬品を用いた湿式処理によって、c)で得られた断片化したフォトレジストを除去する。

(もっと読む)

チタン酸ストロンチウムベースの誘電体層を有するキャパシタを備えたメモリセルの形成方法およびそれから得られるデバイス

【課題】低い等価酸化膜厚(EOT)および低い漏洩電流を有する金属−絶縁体−金属キャパシタを提供する。

【解決手段】低温原子層堆積(ALD)法を用いて、SrxTiyO3ベースの金属−絶縁体−金属(MIM)キャパシタを製造する方法が開示される。好ましくは、下部電極を形成するためにTiNが用いられる。キャパシタのSrxTiyO3誘電体層でのSr/Ti比率は、キャパシタの電気的特性を調整するために変化できる。SrxTiyO3誘電体層の誘電率および漏洩電流は、このSrxTi1−xO3誘電体層のSr含有量とともに単調に減少する。SrxTiyO3誘電体層とTiN下部電極との間の界面でのSr含有量を増加させることによって、界面の等価酸化膜厚(EOT)をさらに低減できる。

(もっと読む)

材料ボンディングのための方法およびシステム

例えば異なる基板(1、4)の上の導電性材料(2、5)の間に、低温および低圧で、信頼性のある電気的接続を実現するためのデバイスおよび方法が開示される。一の形態では、粗くて壊れやすい金属間層(3)が、第1基板(1)の上の導電性材料(2)の上に形成される。他の基板(4)の上の柔らかい半田材料層(6)は、破壊される、壊れやすく粗い金属間層(3)と接触するために使用される。半田材料(6)は比較的柔らかいため、破壊された金属間層(3)と半田材料(6)との間の接続が、表面領域の大きな部分で実現できる。この段階で、第2金属間層(7)が半田材料(6)と第1金属間層(3)との間に形成され、電気的接続を実現する。  (もっと読む)

(もっと読む)

単結晶半導体ナノワイヤの形成

【課題】単結晶ナノ構造を基板の上に成長させる方法を提供する。

【解決手段】基板1の主表面上にパターン2を最初に形成する工程であって、パターン2は基板1の表面まで延びた開口部を有する工程と、パターン2の開口部中の、露出した主表面の上に、金属3を供給する工程と、開口部をアモルファス材料4で、少なくとも部分的に埋める工程と、アモルファス材料4と金属化合物3とを、300℃と1000℃の間の温度でアニールし、金属媒介結晶化により、アモルファス材料4を単結晶材料5に変える工程と、を含む。

(もっと読む)

電子回路および電子回路の製造方法

【課題】ESDダメージが低いESDパワーレベルで発生するFinFET集積回路において、ESDから回路デバイスを保護することができる電子回路を提供する。

【解決手段】電子回路400’は、静電放電現象から保護される少なくとも1つの電界効果トランジスタと、少なくとも1つの保護される電界効果トランジスタ400aとを含む。保護電界効果トランジスタ400bは、保護される電界効果トランジスタ400aの結晶方位とは異なった結晶方位を含む。

(もっと読む)

パターン化エレクトレット構造およびパターン化エレクトレット構造の製造方法

基板(10)上のパターン化エレクトレット構造(21)が誘電体構造を備え、該誘電体構造は、少なくとも1つの非パターン誘電体層(22)と、誘電体構造内、及び/又は、誘電体構造の一部である誘電体層の表面、及び/又は、誘電体構造の一部である誘電体層間の界面における電荷パターン(14)とを含む。非パターン誘電体層(22)の存在により、エレクトレット構造(21)の電荷(14)に対する導電性基板(10)の存在の影響が緩和され、これにより時間に関する電荷安定性を増加させる。さらに、本発明の実施形態において、電荷安定性は、電荷パターンの幅(W1,W2,W3)とは実質的に独立している。こうしたパターン化エレクトレット構造(21)を製造するための方法も提供している。  (もっと読む)

(もっと読む)

有機化合物含有絶縁層の異方性エッチング

【課題】半導体加工において有機化合物含有絶縁層に小さな穴を形成する方法を提供する。

【解決手段】有機化合物含有絶縁層12を、この有機化合物含有絶縁層12上に形成されたレジストハードマスク層13とこのレジストハードマスク層13上に形成されたレジスト層14からなる2重層で覆い、次に、この2重層をパターニングする。そして、反応チャンバー内に、自然エッチングが実質的に避けられるように選ばれる、あらかじめ決められた割合で存在する酸素ガスと窒素ガスとからなる混合気体を流入し、有機化合物含有絶縁層12をプラズマエッチングする。これにより、レジスト層14を部分的に除去しつつ少なくとも一つの穴を形成する。

(もっと読む)

131 - 140 / 302

[ Back to top ]