アイメックにより出願された特許

171 - 180 / 302

メタルラップスルーと改良されたパッシベーションを有する光電池

半導体基板中の光電池デバイスが、放射を受ける表面および裏面、一の導電型の第1領域(29)、反対の導電型を有し表面に隣接する第2領域(20)、および反射防止層(27)を有する。裏面は、バイアの内面も覆う誘電体層(39)により覆われる。表面は電流収集導電性コンタクト(23)を有し、裏面は誘電体を通って延びる導電性コンタクト(31)を有する。表面からの光発生電流のために、導電性パスはバイア中に設けられる。誘電体を全体に有することにより、アラインメントとマスキングが不要となり、同じ誘電体は、絶縁し、半導体の熱保護を提供し、表面とバルクのパッシベーションを助ける。これにより、また、バイア近傍のジャンクション領域が避けられ、望まない再結合電流を低減できる。 (もっと読む)

Cuキャップ層としてCuゲルマナイドおよびCuシリサイドを集積および作製する方法

【課題】周囲の誘電体材料にダメージを与えない銅配線上のキャップ層を形成する方法を提供する。

【解決手段】Cu、N、およびSiおよび/またはGeを含むキャップ層6を、銅の導電構造2の上に形成する方法であって、200℃と400℃との間の温度範囲で、構造をGeH4および/またはSiH4含有雰囲気3に晒すことにより、銅の導電構造2の上に少なくとも1つのキャップ層を形成する工程と、NH3プラズマ処理5を行って、少なくとも部分的に窒化されたキャップ層6を形成する工程と、少なくとも部分的に窒化されたキャップ層6の上に誘電体バリア層7を形成する工程とを含み、少なくとも1つのキャップ層を形成する工程の前に、250℃と450℃との間の温度範囲で、銅の導電構造のプレアニール工程が行われることを特徴とする方法。

(もっと読む)

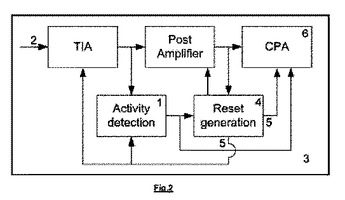

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

量子ドットの製造方法

【課題】基板上の所定位置に少なくとも1つの量子ドットを形成するための良好な方法、リソグラフマスクのための良好な設計、およびこうした設計を作成するための良好な方法を提供する。

【解決手段】半導体材料層を基板(1)上の絶縁層の上に設けることと、半導体材料層をパターニングして、幅(wL)を有する少なくとも1つの半導体材料ライン(2)を基板(1)上に設けることと、水素アニールによって少なくとも1つの半導体材料ライン(2)をパターニングして、基板(1)上の少なくとも1つの所定位置に、少なくとも1つの量子ドット(4)を形成することとを含み、少なくとも1つの半導体材料ライン(2)は、少なくとも1つの量子ドット(4)が形成される少なくとも1つの所定位置において、少なくとも1つのライン(2)の幅(wL)より大きい、20nm〜35nmの振幅(A)を有する局所的な幅変動(3)を有する。

(もっと読む)

設計の最適化

【課題】デバイスの設計または製造プロセスを最適化するのに良好な方法を提供する。

【解決手段】本発明は、デバイスの設計(200)を最適化するための方法(100)に関する。こうした最適化は、予め定めた指標、例えば、デバイス速度、エリア、電力消費または歩留まり等に関して実施される。該方法(100)は、所定のデバイスのための設計(200)を得ることを含む。こうした設計は複数の設計コンポーネントを含む。該方法は、複数の設計コンポーネントから、第2設計コンポーネントよりも予め定めた指標に対してより高い感度を有する第1設計コンポーネント(202)の少なくとも1つのグループを決定することを含む。第1設計コンポーネント(202)は、設計のクリティカルパス上にあることでもよい。該方法(100)は、第1設計コンポーネント(202)を調整することと、第1設計コンポーネントを製造するための製造技術を調整することとを含み、予め定めた指標に関して最適化した設計を取得する。

(もっと読む)

MOSFETデバイスおよびその製造方法

【課題】フェルミレベルのピンニングの効果が、ポリシリコン(Poly−Si)/金属酸化物の界面で高い閾値電圧を招かないMOSFET(金属酸化物半導体電界効果トランジスタ)を含む半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスは、第1MOSFETトランジスタを含む。トランジスタは、基板、基板上の第1high−k誘電体層1、第1high−k誘電体層1上の第1誘電体キャップ層2、および第1誘電体キャップ層2上の、第1ドーピングレベルで第1導電型の半導体材料3からなる第1ゲート電極とを含む。第1誘電体キャップ層2は、スカンジウムを含む。

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

高速トリガーESD保護デバイスおよびその設計方法

【課題】ICに現れるオーバーシュートが低減可能なESD保護デバイス、およびその設計方法の提供。

【解決手段】主ESDデバイス10と、低減された電圧で、ESD電流を流すために、主ESDデバイスのトリガーノードに接続されたトリガーデバイス20とを含むESD保護回路の設計方法。このトリガーデバイス20は、ESD電流のための最初の電流経路中に配置される。この最初の電流経路中に、オフ状態からオン状態にトリガーされる少なくとも1つのトリガー要素を有する。この要素のトリガー速度が考慮され、その設計はそのトリガー速度が増加するように最適化される。更に、少なくとも1つのトリガー要素が、速いトリガー速度を得るために、所定のタイプ、好適にはゲート型ダイオードタイプから選択されESD保護回路。

(もっと読む)

EUVシステムでの汚染検出

【課題】光学システム、例えば、リソグラフシステムにおける汚染を検出するための良好なデバイスまたは方法、そして、こうした汚染検出システムおよび方法を用いたシステムおよび方法を提供する。

【解決手段】応用システム(400)での汚染を検知するためのセンサが開示されている。センサ(100)は、キャップ層(108)を備える。センサ(100)は、センサ(100)を応用システム(400)に設けた場合、キャップ層(108)の上にある最初の汚染層の初期形成時に最初の反射率変化を生じさせるように適合している。最初の反射率変化は、キャップ層(108)上のより厚い汚染層の形成時の平均反射率変化より大きく、システム光学系の実際のミラー上での等しい汚染の形成時での平均反射率変化より大きい。

(もっと読む)

相補ゴーレイシーケンス対を用いて送受信器非理想性を決定し補償するための方法

本発明は、送信器から受信器へ送信されるRF変調信号に関し導入される非理想性特性を決定する方法においてa)既知トレーニングシーケンスを含む前文を生成するステップであって、前文は非理想性特性の評価部分に先行する同期のための同期部分を有し、評価部分トレーシングシーケンスは(i)相補ゴーレイシーケンス対のシーケンスと(ii)非理想性特性の評価のために選ばれた所定の相関関係を満足すべく選択されたシーケンスとを含む、ステップとb)送信器から送信チャネルを経て受信器へ前文を送信するステップとc)受信前文の同期部分の既知トレーニングシーケンスに基づき第1非理想性特性の第1評価を決定するステップとd)第1非理想性特性の第1評価によって受信前文の評価部分を補償するステップとe)所定相関関係を利用して補償された評価部分内の相補ゴーレイシーケンス対により第2非理想性特性の第2評価を決定するステップとを含む。  (もっと読む)

(もっと読む)

171 - 180 / 302

[ Back to top ]