アイメックにより出願された特許

201 - 210 / 302

マルチプレクサ導波路結合方法およびシステム

実質的に異なる所定波長の光に、全光学的にマルチプレクス及び/又はデマルチプレクスを行うための光デバイスが提供される。光デバイスは、基板上に形成された、少なくとも1つの第1誘電体導波路と少なくとも1つの第2誘電体導波路を備え、少なくとも1つの第1誘電体導波路および少なくとも1つの第2誘電体導波路は交差部で交差しており、交差部に形成された回折格子構造を備える。回折格子は、異なる所定波長の光を同じ結合方向に回折するように適合している。結合方向は、格子構造によって規定される平均的な面の法線方向とは異なる。さらに、光学的なマルチプレクスまたはデマルチプレクスを行う方法、そして、実質的に異なる所定波長の光に、全光学的にマルチプレクス及び/又はデマルチプレクスを行うための光デバイスの設計方法が提供される。本発明の実施形態に係る光デバイスは、例えば、ファイバ・トゥ・ザ・ホーム、オフィスまたはカーブの応用など、ローカルアクセス通信において使用できる。  (もっと読む)

(もっと読む)

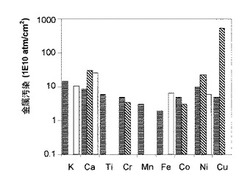

III−V族半導体基板からのバルク金属汚染の除去方法

【課題】III−V族半導体基板からバルク金属汚染を除去するための単一工程の方法を提供する。

【解決手段】該方法は、金属汚染したIII−V族半導体基板を、体積比x:y H2SO4:H2O2(xは3〜9、yは1)を有する硫酸および過酸化物の混合物の中に浸漬することを含む。本発明の実施形態に係る方法を用いてIII−V族半導体基板を処理した後、バルク金属汚染は、基板からほぼ完全に除去できるとともに、処理後の基板の表面粗さは、2μm×2μmの表面グリッドに関して0.5nmRMS未満とすることができる。本発明は、半導体デバイスを製造する更なる処理ステップを実施する前に、本発明の実施形態に係るバルク金属汚染を除去する方法を用いて、半導体デバイスを製造するための方法を提供する。

(もっと読む)

ダメージの入った多孔性誘電体の処理方法

【課題】処理工程で変化した多孔質誘電体層の初期特性を回復させ保持する方法を提供する。

【解決手段】処理された多孔質誘電層であって少なくとも部分的に露出した多孔質誘電層10を上部に有する基板を提供する工程と、処理された多孔質誘電層10の少なくとも露出した部分に薄い水性膜を形成する工程と、表面に水性膜を有する露出した多孔質誘電体膜10を、少なくとも1のシリル化剤と濃縮CO2を含む混合物を含む雰囲気に接触させる工程とを含み、これにより多孔質誘電体10の初期特性を回復させる。

(もっと読む)

非理想トランシーバの較正方法

トランシーバにより信号へ導入される非理想特性の決定方法を提供する。トランシーバは、アップコンバージョン送信機及びダウンコンバージョン受信機を備える。本方法は、a)少なくとも1つの既知のトレーニングシンボルを含む信号を発生するステップと、b)送信機において、第1の周波数を用いて、この信号を第1の信号にアップコンバートするステップと、c)第1の信号を送信機から受信機へ転送するステップと、d)受信機において、第1の周波数とは異なるが第1の周波数にリンクされた第2の周波数を用いて、転送された第1の信号を第2の信号にダウンコンバートするステップと、e)第2の信号内のトレーニングシンボルのうちの少なくとも1つを検出するステップと、f)周波数領域において、検出されたトレーニングシンボルのうちの少なくとも1つの成分のうちの少なくとも1つを分離して非理想の特性を決定するステップとを含む。  (もっと読む)

(もっと読む)

シリサイド化されたゲート電極の仕事関数を調節する方法

【課題】安定し、再現可能な、新しい低仕事関数材料を提供し、さらに再現可能で実行し易い低仕事関数材料の製造方法を提供する。

【解決手段】本発明のシリサイド化されたゲート電極の仕事関数の調節方法は、少なくとも1つのランタニドと、Si、G、またはSiGeを含む半導体材料と、金属を含む層をゲート誘電体上に設けるステップと、前記層をシリサイド化されたゲート電極に変換するステップとを含む。

(もっと読む)

ナノ構造体のドーピング

【課題】本発明は、良好な触媒粒子を用いて、ドープされた細長のナノ構造体を形成するための良好な方法を提供することを目的とする。

【解決手段】本発明は、細長のナノ構造体の成長において使用される触媒粒子を提供する。触媒粒子は、ナノ構造体材料中に実質的に溶解することなく、ナノ構造体材料を含む細長のナノ構造体の成長を促進する触媒化合物と、ナノ構造体材料中に実質的に完全に溶解することにより、成長の間に細長のナノ構造体にドープされる少なくとも1種のドーパント元素とを備える。さらに、本発明は、触媒粒子を使用して、少なくとも1種のドープされた細長のナノ構造体を基板の上に形成するための方法を提供する。当該方法により、細長のナノ構造体においてドーパント濃度を制御することが可能となる。さらに、当該方法により、1017原子/cm3より小さい低ドーパント濃度の細長のナノ構造体を得ることができる。

(もっと読む)

UVリソグラフィシステムおよび方法

【課題】リソグラフプロセスを設定するための良好な装置や方法を提供すること、及び/又は、こうしたリソグラフプロセスで使用するマスクを設計し、そしてリソグラフマスクを製造するための良好な方法およびシステムを提供する。

【解決手段】基板のリソグラフプロセスで使用するリソグラフマスクを設計するための方法(1400)であって、初期位置を有する複数の初期設計構造物を備えたリソグラフマスクのための初期設計を取得すること(1402)と、少なくとも1つのシフトを少なくとも1つの初期設計構造物に適用して(1412)、そこから変更した設計を導出して(1416)、前記所定の照射構成における前記変更した設計に対応したリソグラフマスクを用いて基板を照射する場合のシャド−イング効果を補償することとを含む。

(もっと読む)

2つの仕事関数を備えたCMOSデバイスの製造方法

【課題】本発明は、2つの仕事関数の半導体デバイスの製造方法を提供する。

【解決手段】製造方法は、基板の第1領域及び第2領域上にデバイスを設けることを備える。これは、基板の第1領域及び第2領域上に誘電性層を設けること、及び第1及び第2領域の両方の誘電性層の上部にゲート電極を設けることによってなされる。第1領域上のゲート電極及び第2領域上のゲート電極の両方は仕事関数を有する。上記方法は、さらに、誘電性層とゲート電極との間で第1領域上にキャッピング層を設けることで第1領域上のゲート電極の仕事関数を変更し、及び第2領域における誘電性層とゲート電極との間の界面でスピーシーズを導入するようにスピーシーズを埋め込むことにより第2領域上のゲート電極の仕事関数を変更することを備える。

(もっと読む)

デュアルフリーシリサイドゲートを有する半導体装置の製造方法

【課題】

半導体装置、特にデュアルフリーシリサイド(FUSI)金属ゲートを有するデュアル仕事関数の半導体装置を製造するための良好な方法を提供する。

【解決手段】

デュアル仕事関数半導体装置の製造方法が、第1領域(101a)の第1電極(102a)上に、第1金属層(108)と、少なくとも第1仕事関数変調元素を提供する工程を含む。更に、第2領域(101b)の少なくとも第2電極(102b)上に、第2金属の第2金属層(109)が形成される。第1電極(102a)の第1シリサイド化と、第2電極(102b)の第2シリサイド化とは、同時に行われる。

(もっと読む)

多結晶半導体材料層の低温形成

本発明は、基板(1)の上に多結晶半導体材料層(6)を形成する方法を提供する。この方法は、基板(1)の上に少なくとも1つの触媒粒子(4)を提供する工程であって、少なくとも1つの触媒粒子(4)は少なくとも触媒材料を含み、触媒材料は室温と500℃との間の溶融温度を有するか、または室温と500℃の間の共晶温度を有する触媒材料/半導体材料の合金を形成することができる工程と、500℃より低い温度で、前駆体ガスのプラズマ強化により、基板(1)の上に多結晶半導体材料層(6)を形成し、これにより少なくとも1つの触媒材料(4)を開始剤として用いる工程とを含む。本発明は、更に本発明の具体例にかかる方法を用いて得られた多結晶半導体材料層(6)を提供する。  (もっと読む)

(もっと読む)

201 - 210 / 302

[ Back to top ]