アイメックにより出願された特許

281 - 290 / 302

半導体デバイスに格納された電荷の分布を抽出するための方法

【課題】トラップされた電荷の空間的な分布を決定する必要がある。

【解決手段】パルス上側レベル変化を用いたテスト下で、第1の電荷ポンピング測定をデバイスに実施し、そしてパルス下側レベル変化を用いて第2の電荷ポンピング測定を実施する。得られたデータは、空間的な分布を抽出するために結合される。これは、電荷ポンピング電流Icpの複数の値に対する電荷ポンピングカーブから、空間的な電荷分布の見積もりを再構築して、電荷ポンピング電流Icpと半導体デバイスの計算されたチャンネル長 Lcalcとの間の関係により行う。対応する計算されたチャンネル長Lcalcが半導体デバイスの有効チャンネル長Leffと実質的に等しい値が、前記複数のIcp値から得られ、そして、空間的な電荷分布は、得られたIcpの値を用いて電荷ポンピングカーブから再構築される。

(もっと読む)

不揮発性電荷トラッピングメモリデバイスの動作方法およびプログラミング/消去の状態の決定方法

【課題】不揮発性の電荷トラッピングメモリデバイス、特にNROM(商標名)タイプのデバイスの耐久性および電荷保有特性を改善する必要性がある。

【解決手段】この発明は、プログラミング/消去の状態を決定する方法および、電荷トラッピング半導体デバイスを動作させる方法に関する。プログラミングおよび消去の状態は、第1の正味の電荷分布の(プログラミング状態から消去状態に移行する時の)変化プロフィールが、実質的に第2の正味の電荷分布の(消去状態からプログラミング状態に移行する時の)変化プロフィールの反対となるように、決定される。

(もっと読む)

半導体デバイスに蓄積される電荷の分布の抽出方法

本発明は所定のタイプの電荷トラップ不揮発性メモリデバイスのプログラミング条件セットを決定するための方法に関する。本方法は(a)対応する数のタイプの不揮発性メモリデバイスに適用されるべき異なるプログラミングのパラメータセットを選択するステップと、(b)プログラミングのパラメータセットによって不揮発性メモリデバイスの数をプログラムするステップと、(c)各プログラムされるデバイスの電荷トラップ層の実際の空間的電荷分布を決定するステップと、(d)プログラミングパラメータのうちの少なくとも1つの空間的電荷分布に対する影響を決定するステップと、(e)プログラミングパラメータのうちの少なくとも1つの最適値を決定するステップと、(f)各最適値をプログラミングのパラメータセットに入力しかつステップ(b)からステップ(e)までを少なくとも一度反復するステップとを含む。  (もっと読む)

(もっと読む)

完全ケイ化ゲート形成方法及び当該方法によって得られたデバイス

【課題】各々のトランジスタータイプの金属ゲート電極のWFと閾値電圧とを簡単かつ能率的にコントロールでき、使用されるトランジスタ又はゲート絶縁体のジオメトリ及び/または大きさから独立した、金属ゲートCMOSデバイスの製造方法を提供する。

【解決手段】 半導体デバイスの完全ケイ化ゲート電極を製造する方法は、ゲートスタックの半導体層の上にわたって金属層を形成するステップと、前記半導体層を部分的にケイ化させることができる第1の熱使用量を提供するステップであって、得られた前記ケイ化物層は、金属−半導体の比が1より大きい、ステップと、残存した未反応の金属層を選択的に除去するステップと、前記半導体層を完全にケイ化させることができる第2の熱使用量を提供するステップとを含む。

(もっと読む)

二重の完全ケイ化ゲートを形成する方法と前記方法によって得られたデバイス

【課題】各トランジスタタイプの金属ゲート電極の仕事関数を、簡単で能率的に設計でき、トランジスタ又は使われたゲート絶縁体のジオメトリ及び/または大きさとは関係なくコントロール可能な二重の金属ゲートCMOSデバイスを製造する複雑でない製造方法を提供する。

【解決手段】 二重の完全ケイ化ゲートデバイスを製造する方法は、異なる厚さを有する半導体ゲート電極をそれぞれが有する少なくとも2つのMOSFETデバイスを提供するステップと、前記半導体ゲート電極の各々の上に一定の厚さの金属層を積層するステップと、熱処理を遂行するステップとを含み、前記半導体ゲート電極を完全にケイ化するように、各々の半導体厚さを選択し、それによって前記少なくとも2つのMOSFETは異なる仕事関数を有する。

(もっと読む)

多孔性材料の親水性の定量化のための方法

【課題】 ダメージの深さおよび低誘電率材料の正確な疎水性を割り出すことができる方法が望まれている。さらに、様々な低誘電率材料、特に将来の技術において使用されるであろう超低誘電率材料の開発および選別において使用するための簡単な非破壊の方法へのニーズが存在している。

【解決手段】 多孔性材料の親水性の定量化、ならびに多孔性材料のダメージの深さを割り出すための方法が開示される。典型的な方法は、第1の濡れ角を有する第1の吸着質を使用して、多孔性材料について第1の偏光測定を実行するステップを含んでいる。この典型的な方法は、第2の濡れ角を有する第2の吸着質を使用して、多孔性材料について第2の偏光測定を実行するステップをさらに含んでおり、ここで多孔性材料に対する前記第1および第2の濡れ角が相違している。多孔性材料の親水性が、前記第1および第2の偏光測定に少なくとも部分的にもとづいて判断される。

(もっと読む)

デュアル・ダマシン・パターニング・アプローチ

【課題】半導体素子のビアファーストを用いたデュアル・ダマシン構造のパターニングの方法において、レジスト汚染と低k誘電体絶縁材料の損傷を避けるか、少なくとも最小にする方法を提供する。

【解決手段】低k誘電体絶縁層5にエッチングによりホールを形成し、ホールにギャップ充填材料を堆積し部分的に除去する。この上に金属ハードマスク8と結像材料9を堆積し、トレンチパターンを金属ハードマスクに形成する。結像材料とギャップ充填材料を除去し、金属ハードマスクを用いて無酸素プラズマにより低k誘電体絶縁層をエッチングすることによりトレンチを形成する。トレンチとホールにバリア層と銅を堆積し平坦化する。

(もっと読む)

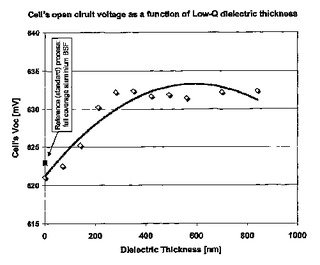

厚いシリコン酸化物とシリコン窒化物の保護層を有する光起電電池とその作製

表面と裏面とを有する基板を提供する工程と、100nmより厚い膜厚を有する誘電体層を裏面に堆積する工程と、誘電体層の上に、水素化されたSiNを含む保護層を堆積する工程と、誘電体層と保護層とを通るバックコンタクトを形成する工程とを含む、例えば太陽電池のような光起電装置の製造方法が記載される。また、表面と裏面とを有する基板を提供する工程と、裏面上に誘電体層スタックを堆積する工程であって、誘電体スタックは、誘電体層のサブスタックを含み、サブスタックは厚さが100nmより厚く、また誘電体層スタックは厚さが200nmより厚くなる工程と、誘電体層スタックを通るバックコンタクトを形成する工程とを含む、例えば太陽電池のような光起電装置の製造方法が記載される。例えば太陽電池装置のような対応する光起電装置が記載される。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法、および得られるデバイス

【課題】半導体デバイス、とくには複数のゲートをフィンガー状に備えるHEMTなどの高周波かつ大電力のデバイスであって、公知の空中ブリッジ構造より小型であり、かつ放熱が要求されるデバイスの製造方法の提供。

【解決手段】高電子移動度トランジスタ(HEMT)などの大電力のデバイスの製造に適しており、ソース・コンタクト間の接続が、空中ブリッジ構造によって製造されるのではなく、半導体層を貫いてビアをエッチングし、デバイスの背面に設けられたコンタクト層に直接接続することにより達成する。

(もっと読む)

フィルム成長開始の強化法

【課題】 化学的に安定した基板表面に、滑らかで一様で、かつ閉じられたフィルム(または層)の形成を許容しない。

【解決手段】 この発明は一般に、集積回路(IC)製作プロセスに関する。この発明は、より特別にはその後の金属、金属酸化物、金属窒化物、および/または、金属カーバイドの層のために、二酸化珪素やシリコン窒化酸化物層などの表面の処理に関する。この発明はさらにこの発明の方法で入手できる高いkのゲートに関する。

(もっと読む)

281 - 290 / 302

[ Back to top ]