Fターム[2F085FF20]の内容

未知の時間間隔を測定するもの (1,604) | 計時制御手段 (305) | 計時制御パルスの位置の検出手段 (22)

Fターム[2F085FF20]に分類される特許

1 - 20 / 22

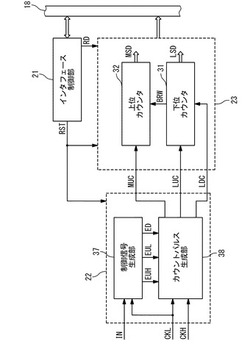

パルス間隔計測回路および半導体集積回路装置

【課題】高精度かつ低消費電力で計測可能なパルス間隔計測装置を提供する。

【解決手段】カウンタ部(23)は、第1アップダウンカウンタ(31)と第2アップダウンカウンタ(32)とを備える。制御部(22)は、第1クロック信号(CKH)と、第1クロック信号(CKH)を分周して生成される第2クロック信号(CKL)と、被測定パルス信号(IN)とを入力し、第1クロック信号(CKH)に基づいて第1カウント信号(LUC)を生成し、第2クロック信号(CKL)に基づいて前記第2カウント信号(MUC)を生成する。制御部(22)は、第2クロック信号(CKL)の1周期より短い期間を測定する第1カウント信号(LUC/LDC)と、第2クロック信号(CKL)の周期に応答して期間を測定する第2カウント信号(MUC)とを生成し、第2カウント信号(MUC)にパルスを生成する期間は第1カウント信号(LUC)の生成を停止する。

(もっと読む)

情報通信端末、生体情報測定機器及び情報通信システム

【課題】無線通信を行う情報通信端末において、汎用無線方式での通信回路の同期信号を利用して、上位層のアプリケーションとしての情報処理の同期を実現すること。

【解決手段】無線通信を行う無線通信部110と、所与の情報処理を行う処理部120と、を含み、前記無線通信部110は、前記外部機器との無線通信の同期を確立するための同期信号を送信して、前記外部機器との無線通信の同期を確立する無線通信同期確立部112と、前記無線通信の同期のタイミングで前記プロセッサーに割り込み信号を出力する処理、又は無線通信の同期のタイミングからの相対時刻をカウントするためのカウント制御処理を行う制御部116とを含み、前記処理部120は、前記外部機器に対する送信情報として、所与のイベントを前記無線通信の同期のタイミングに対応して設定された相対時刻に関連づけたイベント情報を生成する送信情報生成部122を含む情報通信端末100である。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

時間幅測定装置

【課題】時間幅測定における分解能を向上させる。

【解決手段】既知のクロック周波数でクロック信号を発生する基準クロック発生源(2)と、前記クロック信号に基づいて被測定信号をサンプリングして得られたデジタル信号をシリアル/パラレル変換して所定のビット数のパラレル信号を出力するデシリアライザ(3)と、このデシリアライザより出力される前記パラレル信号を記憶するメモリ(4)と、このメモリに記憶された前記パラレル信号に基づいて前記被測定信号に含まれる時間幅を算出する演算回路(5)とを設けた。

(もっと読む)

電力開閉装置の開閉極時間測定装置及び方法

【課題】電力開閉装置の開極時間及び閉極時間を正確に測定することができる開閉極時間測定装置を提供する。

【解決手段】固定接点202と可動接点203とにより電力を開閉する電力開閉装置200に対して、磁気センサ102が電力開閉装置200の接点側可動軸204の軸方向に対する可動接点203の位置を示す磁気センサ出力信号Ss1を出力し、センサ信号測定器103が測定制御指令信号Scの入力時刻を起点として、磁気センサ出力信号Ss1を時系列信号Ssq1として測定しかつ記憶し、開閉極時間測定器104が、電力開閉装置200の開極点又は閉極点において時系列信号Ssq1に出現する変曲点又はピーク点を検出することにより上記開極点又は上記閉極点に達した時刻を検出し、上記起点から上記開極点に達した時刻までの開極時間、又は上記起点から上記閉極点に達した時刻までの閉極時間を測定する。

(もっと読む)

時間計測回路

【課題】TAC方式を使用する時間計測回路、またはTAC方式とパルスカウント方式を組み合わせた時間計測回路において、測定精度を向上させるとともに、デッドタイムのない回路構成を提供する。

【解決手段】入力信号Viの振幅の最大値を検出してトリガTRGを出力するピーク検出回路5と、測定開始信号Vgに応答して動作する3個以上の複数のアナログ信号発生部1〜4と、アナログ信号発生部1〜4の動作タイミングを制御する制御部6と、トリガTRGの出力時点におけるアナログ信号発生部の少なくとも1つの出力電圧を用いて、測定開始信号Vgの出力時刻を起点としたトリガTRGの出力時刻を算定する算定部7とを備えている。

(もっと読む)

光又は電気信号間の時間間隔における変化の検出

【課題】光又は電気信号と光又は電気基準信号との間の時間間隔の変化を検出し、光又は電気信号をフェムト秒まで同期させる方法及び装置を提供する。

【解決手段】光検出器5を用いて光又は電気信号1と光又は電気基準信号3との間の時間間隔ΔTの変化を検出する方法と、光又は電気信号1を光又は電気基準信号3に同期させるための方法を実施する装置とに関する。その方法は、光検出器5によって光又は電気信号1及び光又は電気基準信号3を受け取るステップと、時間間隔ΔTに依存する周波数スペクトルを有する電気応答信号15を光検出器5の出力端子13から出力するステップと、出力された電気応答信号15の周波数スペクトルから選択高調波をフィルタリングにより抽出するステップと、選択高調波の振幅の変化から時間間隔ΔTの変化を検出するステップとを含む。

(もっと読む)

矩形信号の期間幅を予測する回路

【課題】矩形信号のレベルが同一である期間の長さを予測することのできる技術を提供する。

【解決手段】

矩形信号のレベルが同一である期間の長さである期間幅を予測する期間幅予測回路598は、矩形信号のレベルが変化する時間的位置を変化位置として検出する変化位置検出部706と、変化位置から次の変化位置までの長さを期間幅として計測する期間幅計測部594と、期間幅計測部によって計測された複数の期間幅を過去期間幅として記憶する過去期間幅記憶部702,704と、過去期間幅の変化に基づいて、次の期間幅の予測値である予測期間幅RAを算出する予測期間幅算出部710と、を備える。

(もっと読む)

時間測定装置

【課題】複数の時間測定装置を使用せずに安価な手法で測定時間の短縮が可能な時間測定装置を実現する。

【解決手段】クロック信号をカウントすることにより複数の入力信号のエッジ間の時間を測定する時間測定装置において、各エッジを検出した時にどの入力信号で検出されたかの状態を表すイベントデータとトリガ信号を出力するトリガ生成部と、クロック信号に同期して常にカウント動作しトリガ信号が入力される度にカウンタ値を出力するカウンタ部と、イベントデータとカウンタ値を記憶する記憶部と、記憶部に記憶されたイベントデータとカウンタ値を用いてエッジ間の時間を算出する演算制御部とを備える。

(もっと読む)

時間測定回路

【課題】三角波の頂点付近での影響が無く、正確に時間の測定を行うことが可能な時間測定回路を提供する。

【解決手段】一定の周期でクロック信号を発生させるクロック発生手段と、前記クロック発生手段により発生したクロック信号に基づいて、それぞれ互いに所定の位相差を有する第1及び第2のクロック信号を出力する位相クロック出力手段と、前記位相クロック出力手段により出力された第1のクロック信号に従って三角波を発生させる第1の三角波発生手段と、前記位相クロック出力手段により出力された第2のクロック信号に従って三角波を発生させる第2の三角波発生手段と、時間を測定するために用いる被測定パルスを出力するパルス出力手段と、前記パルス出力手段により出力された被測定パルスに応じて、前記第1および第2の三角波発生手段により発生した三角波の振幅をサンプルする振幅サンプル手段と、前記振幅サンプル手段によりサンプルされた三角波の振幅のうちのいずれか1つに基づいて時間を測定する時間測定手段とを備えたことを特徴とするもの。

(もっと読む)

パルス信号時間計測装置

【課題】周波数が可変であるクロック信号発生装置から入力したパルス信号の変化点からの所定の設定値に対応した時間を計測できるパルス信号時間計測装置を提供する。

【解決手段】本発明に係るパルス信号時間計測装置100は、インバータ回路300が出力した入力パルス信号S1を入力し、入力した入力パルス信号S1の変化点を検出して計測開始信号S3を出力する計測開始手段30と、計測開始信号S3の入力により加算を開始し、クロック信号Scのクロック周期毎に加算所定値D1を加算した加算値D2を出力する加算手段10と、加算値D2が設定値Dsに達したとき、計測到達信号S2を出力する計測到達手段20と、加算手段10に上記加算所定値D1を設定する加算所定値算出手段40と、計測到達手段20に上記設定値Dsを設定する制御手段50と、を備えており、計測到達信号S2の出力により、入力パルス信号S1の変化点からの設定値Dsに対応した時間を計測できる。

(もっと読む)

計時装置

【課題】短い時間間隔を計測する。

【解決手段】計時装置は、所定の時間間隔でカウント値を更新するカウンタと、入力信号に応じて、カウンタのカウント値を取りこむキャプチャ回路と、記憶指示信号に応じて、キャプチャ回路に取りこまれたカウント値を記憶する記憶回路と、入力信号に応じて、記憶指示信号を生成する指示信号生成回路と、を備える。

(もっと読む)

競技用計時システム、無線機器、および、タイム送信方法

【課題】キャリアセンスが行えない状況でも、コリジョンの発生を抑制しつつ、競技者個々の競技タイムを適切に計時できる競技用計時システム等を提供する。

【解決手段】各無線タグ60は、予め3つのグループ(A,B,Cグループ)に分けられている。そして、グループ毎に、互いに素となる通信間隔(2,3,5)を空けて通信(タイム情報の送信)が行われる。つまり、Aグループの無線タグ60は2α(α=1回の通信時間)、Bグループでは3α、そして、Cグループでは5αだけ、通信間隔を空けて通信を行う。また、各無線タグ60は、それぞれ合計3回に亘って通信を行う際に、1回目と2回目の通信は、第1のチャンネルを使用するが、3回目の通信は、第2のチャンネルを使用する。なお、チャンネルを変更して行う3回目の通信は、通信間隔を待たずに、変更直後(通信時間αの周期上)に開始する。

(もっと読む)

遅延時間評価方法及び回路、及び半導体装置

【課題】本発明は、遅延時間評価回路及び半導体装置に関し、遅延測定対象回路と遅延時間評価回路の独立性、即ち、非干渉性を向上することを目的とする。

【解決手段】複数段のゲート回路から構成されており接続段数が切り替え可能である被測定回路内の信号の伝播遅延時間を評価する遅延時間評価回路において、入力信号と、この入力信号を接続段数が任意の段数に切り替えられた被測定回路を通した信号の位相差を検出する位相差検出回路と、位相差に応じたパルス列を生成して外部へ出力する変換回路部と、被測定回路と位相差検出回路との間を容量結合又は非接触結合により結合する結合部とを備えるように構成する。

(もっと読む)

タイヤに備え付けられたセンサの注目に値する角度位置を計時する方法

【課題】タイヤに備え付けられた少なくとも1つのセンサの注目に値する角度位置を計時する方法を提案する。

【解決手段】本発明は、外部基準系に対して回転するタイヤ(10)に備え付けられた少なくとも1つのセンサ(12)の注目に値する角度位置(Qr)を計時する方法であって、センサ(12)からの出力信号(s(t))からタイヤ(10)の一回転中に注目に値する極値を与えるのに適した基準信号(sr(t))を生成するステップと、センサの元々の角度位置(Q0)の時刻(t0)を基準信号の注目に値する極値の時刻であると決定するステップと、元々の角度位置の時刻に対する注目に値する角度位置(Qr)の時刻(tr)を決定するステップとを有することを特徴とする方法に関する。

(もっと読む)

光子検出器

本発明は測定電子の光子誘発トリガーするための光電陰極を備えた光子検出器に関している。少なくとも一つの一次元電子検出器ピクセル配列が空間的位置情報をもたらす。電子光学部品ユニットは、測定電子を当該配列にガイドするために用いられる。各ピクセル(19)は、ピクセル(19)のアナログ測定信号をデジタル測定信号に変換するための、バックグラウンド抑制用ディスクリミネータを備えた電子コンバータユニット(20)を有している。電子後処理ユニット(39)はデジタル測定信号を処理するために用いられる。各ピクセル(19)のコンバータユニット(20)は、少なくとも一つのクロック発振器(36)、並びにクロック発振器(36)と信号接続している少なくとも一つのカウンタ(29、30)、及び、デジタルタイミング信号を発生するためのディスクリミネータ(27)を有する。タイミング信号は、時間基準点と、ディスクリミネータ(27)によって抑制されなかったアナログ測定信号の到着時間(t測定)との間の、クロック周期の数から生じるようになっている。こうして、光子検出器において、測定信号から位置情報だけが得られるのではなく、加えて、与えられたピクセルにおいて測定信号がトリガーされたときの情報も得られるようになる。  (もっと読む)

(もっと読む)

パルス幅計測装置及び画像形成装置

【課題】本発明は、基準クロック信号を逓倍した高速クロック信号や温特の悪い素子を使用することなく、安価な回路構成で、より正確にパルス幅を測定できるパルス幅計測装置を提供する。

【解決手段】入力されたパルス信号のパルス幅を基準クロック信号に基づいて計数する。基準クロック信号と位相の異なるパルス信号を、パルス幅を可変する位相データに基づいて生成し、生成されたパルス信号を利用して、入力されたパルス信号のパルス幅の後端の変化点を検出する。変化点が検出されたときに生成されたパルス信号の位相データと計数された結果とを用いて、入力されたパルス信号のパルス幅を算出する。

(もっと読む)

時間計測回路

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

遅延時間評価方法及び回路、及び半導体装置

【課題】本発明は、遅延時間評価回路及び半導体装置に関し、回路面積を増大させることなく、少数段で構成されるゲート回路等の遅延時間を短時間で精度よく評価することを目的とする。

【解決手段】複数段のゲート回路から構成されており接続段数が切り替え可能である被測定回路内の信号の伝播遅延時間を評価する遅延時間評価回路において、入力信号と、この入力信号を接続段数が任意の段数に切り替えられた被測定回路を通した信号の位相差を検出する位相差検出回路と、位相差に応じたパルス列を生成して外部へ出力する変換回路部とを備え、パルス列のパルス数は被測定回路内での入力信号の遅延時間に相当するように構成する。

(もっと読む)

検出イベントの時間分解記録のための検出器

【課題】本発明は、検出イベントの時間分解記録のための検出器に関する。

【解決手段】検出器は、検出イベントが発生するときに、動作状態で電気信号を供給する変換装置(34、35、36)、及び変換装置(34、35、36)に結合され、電気信号に時間的に割り当てられたトリガ信号(5)を供給するように設計された少なくとも一つのトリガ(3)と、第一のアナログ時間信号(Z1)を供給する少なくとも一つの時間信号発生源(10)と、トリガ(3)に結合され、第一のアナログ時間信号(Z1)の、トリガ信号(5)に時間的に割り当てられた第一の瞬間値(E1)を供給するよう設計された少なくとも第一のサンプル採取器(6)とを有する評価電子機器を有する。  (もっと読む)

(もっと読む)

1 - 20 / 22

[ Back to top ]