Fターム[2G132AA08]の内容

Fターム[2G132AA08]の下位に属するFターム

ROM、不揮発メモリ、磁気バブル (130)

Fターム[2G132AA08]に分類される特許

1 - 20 / 601

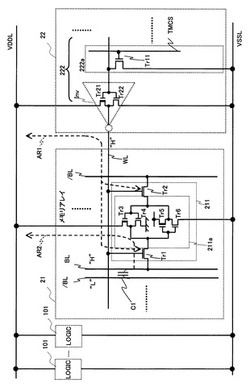

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

半導体装置およびその検査方法

【課題】ウエハ検査時に必要なプローブピンを削減可能にした半導体装置を提供する。

【解決手段】第1のデータを記憶する記憶素子と、データ読み出しの指示が入力されると、記憶素子から第1のデータを読み出して出力するデータ入出力制御部と、データ入出力制御部から出力される第1のデータを第1の端子に出力し、第1のデータを第1の端子に出力するとき、自装置の第2の端子と他の半導体装置の第1の端子とを接続するプローブカードを介して他の半導体装置から受信する第2のデータを保持し、その後、第2のデータを自装置の第1の端子に出力するデータラッチ部とを有する。

(もっと読む)

DDR信号をテストするための補助冶具

【課題】マザーボードのDDR信号を容易にテストすることができるテスト補助冶具を提供すること。

【解決手段】本発明に係るDDR信号をテストするための補助冶具は、DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備え、前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリ用コネクタのピンの名称或いは機能をそれぞれ示す。

(もっと読む)

半導体メモリ装置及びそのためのテスト回路

【課題】本発明は、テスト速度を向上させることができる半導体メモリ装置及びそのためのテスト回路に関するものである。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

(もっと読む)

半導体メモリ装置および半導体システム

【課題】PVT変動によってスキューが発生しても、不良に関する情報を適切に格納できるようにした半導体メモリ装置を提供する。

【解決手段】書き込み動作のために書き込みコマンドおよびデータを印加し、読み出し動作のために読み出しコマンドを印加し、前記読み出し動作によって出力データが入力されるテスト回路と、前記書き込みコマンドに応答して前記データをメモリセルに格納し、前記読み出しコマンドに応答して不良に関する情報を含む情報データを内部的に格納するが、前記情報データの格納は、前記情報データのレベルが遷移する場合に発生するパルスに同期して行われる。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

不揮発性半導体記憶装置及びその試験方法

【課題】電源投入により自走的にメモリセルアレイの動作テストを実行する。

【解決手段】一つの実施形態によれば、不揮発性半導体記憶装置は、不揮発性半導体記憶装置は、ロムヒューズブロックを有するメモリセルアレイ、自走テスト部を有するコントローラ、及びコマンドレジスタを有する。不揮発性半導体記憶装置は、電源投入によりメモリセルアレイの自走テストを実行する。

(もっと読む)

集積回路及び不揮発性記憶装置書き換え方法

【課題】不揮発性記憶装置内の制御プログラムの書き換え時間を短縮すること。

【解決手段】バウンダリスキャン回路は、不揮発性記憶装置に接続された第1バウンダリスキャンレジスタ装置、及び、不揮発性記憶装置に接続されない第2バウンダリスキャンレジスタ装置を含む回路であって、第1バウンダリスキャンレジスタ装置及び第2バウンダリスキャンレジスタ装置の双方を経由する第1経路と、第1バウンダリスキャンレジスタ装置を経由し第2バウンダリスキャンレジスタ装置を経由しない第2経路とが切り替え可能に接続される。制御信号回路は、TAPコントローラからバウンダリスキャンレジスタ装置に入力される制御信号の入力経路が、第1経路又は第2経路の切り替えに応じて切り替え可能に接続される。

(もっと読む)

集積回路,集積回路の試験装置および集積回路の試験方法

【課題】集積回路上の冗長メモリの試験に際し、冗長メモリにおける不良発生位置を取得する。

【解決手段】スペアのメモリセルをもつ冗長メモリ30と、冗長メモリ30に与えるテストパターンと当該テストパターンを冗長メモリ30に与えた際に冗長メモリ30から出力されるべきデータの期待値とを生成する生成部41と、生成部41によって生成された期待値と、第1生成部41によって生成されたテストパターンを冗長メモリ30に与えた際に冗長メモリ30から出力されるデータとを比較する比較部42と、比較部42の比較結果を記憶する記憶部10と、比較部42の比較結果が不一致である場合、当該比較結果を、当該比較結果を得た冗長メモリ30の位置情報に対応付けて記憶部10に書き込む一方、比較部42の比較結果が一致である場合、当該比較結果の記憶部10への書込を抑止する書込制御部50Aと、を有する。

(もっと読む)

半導体記憶装置

【課題】メモリセルのサブスレッショルド・リーク電流の影響によって不良となるデバイスを選別検査で確実にリジェクトする。

【解決手段】行列状に配置された複数のメモリセルMEMと、メモリセルの行に対応して設けられた複数のワード線WL0〜WL4と、メモリセルの列に対応して設けられた複数のビット線対BT0、BB0及びBT1、BB1と、前記複数のワード線のうち、検査対象の注目メモリセル以外の非注目メモリセルが接続された非注目ワード線をフローティングとするスイッチMN1と、前記非注目ワード線がフローティングのときに、当該非注目ワード線を昇圧するポンピング回路POC0とを備える。

(もっと読む)

半導体装置

【課題】誤ってテストモードにエントリされたとしても、正常に動作させる。

【解決手段】半導体装置は、内部回路をテストするテスト回路2に対してテストを開始させるテストモードエントリ信号が入力されたことに応じて、内部のラッチ10をセットすることにより、テスト回路2に対し、テスト回路2の駆動を許可するテストイネーブル信号をラッチ10から出力するテスト信号発生回路1を備える。テスト信号発生回路1が、ラッチ10がテストイネーブル信号を出力している場合、テストイネーブル信号を遅延させて、ラッチ10をリセットするリセット信号を生成するリセット信号生成回路30と、ラッチ10がテストイネーブル信号を出力している場合に、外部から供給されるトグル信号に基づいて、リセット信号生成回路30によるリセット信号を生成する動作を初期化する遅延初期化信号を出力する遅延初期化回路40と、を有している。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

メモリシステム

【課題】

実施形態は、制御部をテスト可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、前記NAND型フラッシュメモリと前記入出力部との間、および前記NAND型フラッシュメモリと前記入力バッファ部との間に設けられた複数のデータバスと、入力される選択信号に基づいて、所望の前記データバスを選択するスイッチと、前記NAND型フラッシュメモリ、前記入出力部、及び前記スイッチを制御して、前記入力バッファ部から前記NAND型フラッシュメモリにデータを書き込むとき、選択された前記データバスを介して、前記NAND型フラッシュメモリと前記入力バッファ部との間を接続し、残りのデータバスを介して、前記NAND型フラッシュメモリと前記入力バッファ部との間を接続しない前記選択信号を前記スイッチに出力する制御部とを含む。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】不良電流パスの選別に要する時間を短縮する。

【解決手段】半導体装置は、それぞれ少なくとも1つの貫通電極を含み、インターフェイスチップ内に第1のノードn1を有する複数の電流パス101Xと、互いに異なる複数の電圧値からなる比較電圧DACOUTを生成する比較電圧生成部102と、複数の電流パス101Xそれぞれの第1のノードn1の電圧TSVCXと、比較電圧DACOUTの上記複数の電圧値それぞれとを比較し、比較の結果を示す比較結果信号CMPXを電流パス101Xごとに出力する比較部103と、比較結果信号CMPXに応じて、複数の電流パス101Xのそれぞれが高抵抗化しているか否かを示す結果信号RESLTXを生成する結果信号生成部104とを備える。

(もっと読む)

半導体装置

【課題】

実施形態は、ベリファイ動作の誤判定を低減可能な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、メモリセルを含むメモリセルアレイと、ビット線と、センスアンプと、制御部とを備え、センスアンプは、外部から入力された第1又は第2テストデータと第1又は第2ページのメモリセルに保持された保持データとを比較するテスト工程で、第1テストデータと第1ブロックの第1ページに対応する保持データとを比較した後に、第1テストデータと第2ブロックの第1ページに対応する保持データとを比較し、第1テストデータとは異なる第2テストデータと第1ブロックの第2ページに対応する保持データとを比較した後に、第2テストデータと第2ブロックの第2ページに対応する保持データとを比較することを特徴とする。

(もっと読む)

半導体装置

【課題】テスト時間の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】このチャージポンプ回路12では、通常動作時は、ポンプキャパシタC0,C2の一方電極にポンプクロック信号φPを与えるとともにポンプキャパシタC1,C3の一方電極にポンプクロック信号φPの相補信号を与え、ポンプキャパシタC0〜C3の欠陥を検出するテストモード時は、ポンプキャパシタC0〜C3の各々の電極間に外部電源電圧VCCを静的に印加する。したがって、MOSトランジスタのオン耐圧を超える高電圧をポンプキャパシタC0〜C3に印加できるので、テスト時間を短縮化できる。

(もっと読む)

試験管理装置

【課題】試験の信頼性を低下させることなく、試験時間を短縮する。

【解決手段】試験リスト保持部12は、被試験対象物に実施すべき複数の試験項目とその順番を規定した試験リストを保持する。対応テーブル保持部13は、各試験項目の結果値をランク分けし、各ランクと、省略または追加する試験項目とを対応付けたテーブルを保持する。試験結果値取得部22は、試験リストにしたがい実施された試験項目の試験結果値を取得する。ランク判定部23は、対応テーブル保持部13を参照して、試験結果値取得部22により取得された試験結果値をランク分けする。試験リスト管理部24は、ランク判定部23により決定されたランクに応じて試験リストの内容を適応的に変更する。

(もっと読む)

半導体集積回路テスト方法

【課題】複数のメモリを備えた半導体集積回路において、IRドロップによる誤動作を回避しつつ、効率の良いメモリテストを実現すること。

【解決手段】半導体集積回路に含まれる複数のメモリのそれぞれを単体でテストした場合に消費される電流を参照し、該複数のメモリから同時にテストすべき複数のメモリを被テストメモリとして選択する工程と、前記複数の被テストメモリを同時にテストした場合に消費される総消費電流をシミュレーションにより生成する工程と、前記総消費電流および前記半導体集積回路のレイアウト情報に基づいて、前記半導体集積回路におけるIRドロップを算出する工程と、算出した電圧降下が所定の許容値以内であるか否かを判定する工程と、前記電圧降下が前記所定の許容値を超えた場合には、前記複数のメモリから同時にテストすべきメモリを再度選択し直す工程と、を含む。

(もっと読む)

半導体装置

【課題】複数の半導体チップが積層された構造を有する半導体装置において、パンプ電極BP_0に接触せずに、かつ、貫通電極TSV_0の負荷容量を増やさずにテストできる半導体装置10を提供する。

【解決手段】積層された複数の半導体チップ21〜24のそれぞれが、バンプ電極BP_0と、テストパッドPAD_0と、テストパッドから供給される信号を受け取りバンプ電極に供給するテストバッファTD_0と、テストバッファの活性状態と非活性状態とを制御する制御信号を供給するバッファ制御部BCとを含む。

(もっと読む)

1 - 20 / 601

[ Back to top ]