Fターム[2G132AB20]の内容

Fターム[2G132AB20]に分類される特許

41 - 60 / 107

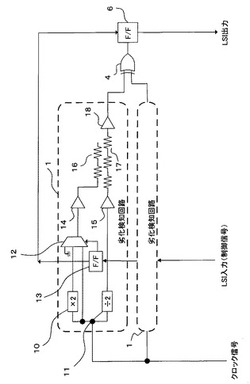

劣化検知回路及び半導体集積回路

【課題】出荷後のLSIにおけるエレクトロマイグレーション劣化現象を検知することが可能な半導体集積回路を提供する。

【解決手段】エレクトロマイグレーション現象による配線劣化を検知する劣化検知回路(1)をN(但し、Nは、2以上の整数)個含んで構成する半導体集積回路であり、劣化検知回路(1)は、クロック信号を入力し、当該クロック信号の2倍の周波数を持つ倍周信号を生成する倍周回路(10)と、クロック信号の半分の周波数をもつ分周信号を生成する分周回路(11)と、分周信号を入力し、配線劣化を検知するテスト回路(17)と、倍周信号を入力し、テスト回路(17)を加熱するヒータ回路(16)と、を有することを特徴とする。

(もっと読む)

故障診断装置

【課題】基板上の集積回路に搭載された境界走査試験回路の一部のレジスタをシフトレジスタとして動作させ、通常動作時に、出力側の一部の出力信号を入力側にフィードバックして比較して、信号異常が検知できる故障診断装置を提供する。

【解決手段】複数の集積回路の前段の集積回路から入力される入力信号を走査する第1の走査回路と、後段の集積回路に出力する出力信号を走査する第2の走査回路と、各集積回路に設けられたテスト端子を介して第1及び第2の走査回路を制御し、各走査回路の出力信号に基づき各集積回路の検査を行う検査回路と、各集積回路の少なくとも1つの集積回路に設けられ、通常動作時に、後段の第2の走査回路からテスト端子を介して入力された出力信号と、自集積回路の第1の走査回路の出力信号とを比較する比較回路と、比較回路の比較出力に基づき自集積回路の異常を通常動作時に検出する異常検出回路とを具備する。

(もっと読む)

テスター装置

【課題】ウエハーに形成されている被試験デバイスに供給する信号や電源の異常から、被試験デバイスを保護する機能を有するテスター装置を提供する。

【解決手段】ウエハーに形成されている被試験デバイスのテストを行うテスター装置であって、ウエハーに形成されている被試験デバイスに供給する電源を監視し、電源の異常があった場合に、これを検出する、電源異常検出回路と、ウエハーに形成されている被試験デバイスに供給する信号を監視し、信号の異常があった場合に、これを検出する、信号異常検出回路と、前記電源異常検出回路が電源の異常を検出した場合、及び/又は、前記信号異常検出回路が信号の異常を検出した場合に、被試験デバイスへの電源の供給と信号の供給を停止する、供給停止回路とを、備えて構成されている。

(もっと読む)

半導体集積回路および電子機器

【課題】内部信号を逐次信号に変換して出力するLSIにおいて、LSI外部信号と同期をとって観測することを可能にすること。

【解決手段】内部信号線群から1以上の内部信号線を選択する内部信号選択部1004と、内部信号線群から所定の方法により基準信号線を選択する基準信号選択部1005と、内部信号と基準信号をサンプリングするクロックを選択する基準クロック選択部1006と、出力クロックを選択する出力クロック選択部1008と、内部信号と基準信号とを基準クロックによりサンプリングするサンプリング部1007と、サンプリングした各信号値を前記出力クロックの各サイクルで逐次出力する逐次信号出力部1009とを備え、外部基準信号と内部基準信号の位相差を比較することで、逐次変換処理による遅延時間を考慮することが可能となるので、内部信号と外部信号の同期をとる事ができる。

(もっと読む)

計測システム

【課題】ポーリング処理による複数回のアクセスの場合にも、モニタ機能の低下を防止することが可能な計測システムを提供する。

【解決手段】計測システム100は、計測バス130を監視しコントローラ110から計測カード140に対して1回アクセスする毎に、モニタメモリ122bを参照してアクセスした内容と同じ内容を示すデータが記憶されているか否かを検出する。検出された場合には、この同じ内容を示すデータに対応付けられたカウント数を1インクリメントし、検出されない場合には、アドレスとカウント数の初期値を発生させてアクセスした内容を示すデータと対応付けてモニタメモリ122bに順次記憶させる。

(もっと読む)

電子機器の試験システム

【課題】電子機器の試験状況を、2方向から見ても実際の被試験機の配置通りに、文字、

色情報を付記して一画面で表示する。

【解決手段】被試験機200の試験プログラム202を実行する冶具パソコン201とネ

ットワーク208で接続されたサーバ209上に、全被試験機の試験状況情報210を保

持する。試験状況変更時、試験プログラムが被試験機の試験状況情報を更新する。試験状

況表示プログラム203は、表示間隔情報206で指定された間隔毎に全被試験機の試験

状況情報を読み込む。試験状況表示プログラムは、実行開始時に冶具パソコン番号207

を読み込む。冶具パソコン番号より、方向情報204が一意に決定され、この方向情報よ

り配置情報205も一意に決定される。配置情報に従って配置された被試験機を表した枠

内に、読み込んだ被試験機の試験状況情報を、対応する被試験機の枠内に表示する。

(もっと読む)

半田バンプの高感度抵抗測定装置及び監視方法

【課題】温度変化による抵抗変化を含まずに半田バンプ接続部の微小な抵抗変化を高い分解能により正確に検出可能とする。

【解決手段】マザーボード10に実装されたBGAパッケージ12について、変形応力によるダメージを受け易い監視バンプ20−11と、変形応力によるダメージを受けにくい基準バンプ20−12を選択し、監視バンプ20−11に第1定電流源30から一定電流を流すと共に、基準バンプ20−12に第2定電流源32から同じ値の一定電流を流す。半田バンプ抵抗測定装置28は、第1定電流源30からの一定電流により監視バンプ20−11に発生する第1電圧から第2定電流源32からの一定電流により基準バンプ20−12に発生する第2電圧を差し引いた差電圧を、監視バンプ20−11の抵抗変化を表す抵抗変動電圧として直流電圧計34に表示する。

(もっと読む)

制御装置

【課題】本発明は、制御装置の演算部のプロセッサコアとその自己診断装置の自己診断を可能とし、運転中でもバウンダリスキャン検査が可能で、演算部のプロセッサコアの故障箇所の自己修復が可能な制御装置を提供することを目的とする。

【解決手段】バウンダリスキャンバス12に接続される2つのプロセッサコア(2a、2b)を有する演算装置2を備える制御装置1であって、

前記プロセッサコアは、前記プロセッサコアの診断を、時分割で、相互にバウンダリスキャン検査によって診断することを特徴とする制御装置。

(もっと読む)

基板診断方法

【課題】

従来技術では、CPUの動的な内部異常による故障部位の特定は困難な状況であった。

【解決手段】

複数のCPUが搭載されたプリント回路基板を診断する方法であって、前記複数のCPUは各々、内部処理中に異常となった場合の例外処理を検出するエラー検出部と、エラー発生時のエラーデータをバウンダリスキャンチェーン経由で出力するための出力部と、複数のCPUのデータをシリアル出力するためのライト制御信号を生成及び出力する他CPUエラー検出部と、を有し、前記複数のCPUに対して、前記バウンダリスキャンチェーンを制御するバウンダリスキャン制御部と、前記複数のCPUから出力されたデータを基に解析および結果を表示するエラー解析部と、を有するバウンダリスキャンコントローラを用いて、監視動作時のデータをバウンダリングスキャンチェーンで監視して、エラー検出および解析を行うことを特徴とする基板診断方法を提案する。

(もっと読む)

チップ内電位モニター回路

【課題】チップ内部の特定の箇所の電位を精度よく測定することのできるチップ内電位モニター回路を提供する。

【解決手段】チップ内電位モニター回路1は、半導体集積回路チップ100の電源端子200から供給されるVDD電源配線上のノードN1における内部電位VDDMが入力されるADコンバータ11と、ADコンバータ11でデジタル値に変換された内部電位VDDMの値が出力されるモニター出力端子12と、ADコンバータ11のみが接続される専用電源端子13と、を有する。

(もっと読む)

半導体試験装置

【課題】テストプログラムの違反の未検出を防止し、DUTのトラブルの発生を防止することが可能な半導体試験装置を提供する。

【解決手段】半導体試験装置100では、テストプログラム実行部120によるテストプログラムの実行中に電源チェッカ機能を実現し、電源チェッカ制御部110は、違反条件データを違反条件チェック部124に出力し設定する。テストプログラムについて生成した設定データを違反条件チェック部124に設定し、違反条件データに基づいて設定データをチェックし、テストプログラムの違反を検出する。違反を検出した場合にはテストプログラムの実行を停止させ画面表示する処理を行う。

(もっと読む)

半導体集積回路

【課題】回路規模を拡大することなく、高周波成分を含む電源ノイズを観測すること。

【解決手段】半導体集積回路200は、自身を動作させるための電源の電源電圧と所定の基準電圧とを比較する電圧比較部220と、電圧比較部220の比較結果を記録する比較結果記録部250とを備え、比較結果記録部250は、クロック信号を基準として、電圧比較部220において電源電圧が基準電圧を超過していると判定された期間の長さを記録し、この記録結果を外部から取得させることで電源ノイズの観測を行わせる。

(もっと読む)

電位変動検出装置

【課題】集積回路の内部配線に生じた電位変動の絶対値を簡便に測定可能な電位変動検出装置を提供する。

【解決手段】電位変動検出装置は、内部配線、基準電圧を供給するための内部配線とは独立して配線された基準電圧供給配線、及び内部配線上の所定箇所の電位と基準電位供給配線の電位の差に応じた信号を出力する電位比較部を有する集積回路と、基準電圧供給配線に基準電圧を供給する電源部と、電位比較部から出力された信号の電圧を測定する電圧測定部と、電源部を制御して、電圧測定部によって測定された電圧に応じて基準電圧の値を制御する制御部と、を備える。制御部は、電圧測定部によって測定された電圧に基づいて内部配線に生じる電位変動を検出し、電位変動を検出した際の電源部が供給する基準電圧を所定箇所の絶対電圧値として測定する。

(もっと読む)

半導体検査装置の制御方法

【課題】電源電圧が降下変動しても測定の信頼性が損なわれることなく、検査を行うことができる半導体検査装置の制御装置を提供する。

【解決手段】コントローラ、及び、電源投入回路の電源として、電源電圧の低下に対し出力電圧を維持できるよう設計されたスイッチングレギュレータを用いるとともに電源電圧の低下を検出する手段を設け、測定中に電源電圧の低下を検出した場合、自動的に測定を停止し、電源電圧が復帰した後に自動的に再測定を実施する。

(もっと読む)

集積回路

【課題】本発明は、集積回路において、該集積回路が動作モードである時に境界試験を行うために使用することができる境界試験アーキテクチャを提供する。

【解決手段】本発明の集積回路で使用する試験アーキテクチャは、所望の機能を実行する、入力データをキャリーする入力端子及び出力データをキャリーする出力端末を有する集積回路のアプリケーション論理回路(20)と、集積回路のレジスタで形成されたシリアル走査経路であり、走査経路から連続的にロードされた比較データを保持するための少なくとも一つの比較データ・レジスタ(98)を含む該シリアル走査経路と、比較データ・レジスタの比較データとアプリケーション論理回路のデータとを比較することに応じて比較信号(CTERM)を生成する、アプリケーション論理回路及び比較データ・レジスタに接続された比較論理(COMPOUT)とを備えている。

(もっと読む)

自らのチップ識別情報の読み取りを行える情報出力装置、チップ識別情報記録部を有する半導体集積回路、およびチップ識別情報の読み出し方法

【課題】専用の読み取り装置に接続することなく自らのチップ識別情報の読み取りを行なえる情報出力装置、チップ識別情報記録部を有する半導体集積回路、およびチップ識別情報の読み出し方法の提供。

【解決手段】情報出力装置100は、半導体集積回路110及び出力装置120を有している。半導体集積回路110は、プロセッシング回路111に入力された情報を処理して出力装置120に出力する回路である。また、半導体集積回路110は、半導体集積回路110に関する識別情報132を記録するチップ識別情報記録部112を有するとともに、プロセッシング回路111によって処理された処理情報134または識別情報132を選択して出力装置120に出力する切り替え回路113を有している。切り替え回路113が識別情報132を選択すると、識別情報132が出力装置120に出力される。

(もっと読む)

劣化診断回路及び半導体集積回路

【課題】単純な回路で構成される劣化診断回路及びIPコア化された劣化診断回路が組み込まれた半導体集積回路を提供する。

【解決手段】半導体集積回路10a内に設けられた実回路12の経年劣化による故障時期を予測する劣化診断回路13aであって、一定の周波数でパルス信号を出力する信号発生回路14と、実回路12と同時期に設けられ、信号発生回路14により出力されたパルス信号を通過させて出力する劣化診断対象回路16aと、信号発生回路14により出力されたパルス信号の立ち上がりから所定時間だけ遅れて立ち上がりかつ信号発生回路14により出力されたパルス信号と同じ周波数を有するクロック信号を生成するとともに、劣化診断対象回路16により出力されたパルス信号のタイミングとクロック信号のタイミングとを比較して劣化診断対象回路16aの劣化が発生したか否かを判定し、判定結果を実回路と外部との少なくとも一方に出力する劣化判定回路18とを備える。

(もっと読む)

半導体集積回路装置

【課題】消費電力を低減できる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、内部電源発生回路と、半導体メモリと、前記半導体メモリの不良情報を記録する記憶回路33と、前記不良情報が読み出された場合に、前記内部電源発生回路から発生する内部電源を停止するように構成された制御回路39とを具備する。

(もっと読む)

半導体集積回路装置及び制御システム

【課題】パルス波形の立ち上がり時間と立ち下がり時間とを独立して測定することが可能な半導体集積回路装置を提供することを目的とする。

【解決手段】被測定セルMCと波形整形セルWCとが直列に接続された回路部が複数リング状に接続されたリングオシレータを備え、各々の波形整形セルは同一のリセットノードNDに共通接続されており、リセットノードが第1のレベルにあるとき全ての波形整形セルはリセット状態になり、リセットノードが第2のレベルにあるとき波形整形セルはそれぞれ前段の被測定セルからの出力を後段に伝播する伝播状態になり、リセット状態と伝播状態とが交互に切り替わることを特徴とする。

(もっと読む)

動的基板診断用基板

【課題】

従来のバウンダリスキャンの利用では、シリアルバス接続によるデイジーチェーン構成としており、転送速度が遅く、プロセッサやLSIの動作とは別クロックで動作するため、稼動状態での誤動作・故障の検出が難しい。

【解決手段】

本発明は、複数のプロセッサと各種LSIが搭載されたプリント基板において、前記LSIの動作状態を取得する手段と、この取得結果を記憶する手段とを有する診断制御部を設ける。また、その取得結果とプロセッサの動作状態を取得する手段と、該取得結果を記憶する手段を設けた上で、該データを同一時間字軸で時系列に管理、保存する手段を設け、プロセッサの動作状態と前記LSIで取得した結果を元に運用状態における故障要因、部位の特定を行う解析手段を設けて動的基板診断方式を実現する。

(もっと読む)

41 - 60 / 107

[ Back to top ]