Fターム[2G132AD03]の内容

Fターム[2G132AD03]に分類される特許

1 - 20 / 95

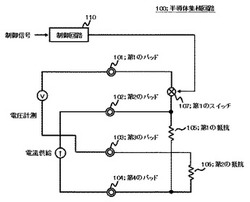

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

電圧出力装置および抵抗測定装置

【課題】半導体スイッチを介して測定対象体に対する測定用電圧の出力をオン・オフする構成において、スパイク電圧を大幅に低減する。

【解決手段】規定電圧値V1の測定用電圧Vmを測定対象体21に出力する電圧出力装置1であって、測定用電圧Vmを出力すると共に測定用電圧Vmの電圧値を制御可能な電源部2と、電源部2から出力される測定用電圧Vmの測定対象体21に対する出力をオン・オフする半導体スイッチ3aと、電源部2および半導体スイッチ3aを制御する処理部5とを備え、処理部5は、半導体スイッチ3aをオフ状態に制御した状態において電源部2に対する制御を実行して測定用電圧Vmの電圧値を段階的に複数回に亘って変化させて規定電圧値V1に設定する電圧設定処理、および半導体スイッチ3aをオン状態に制御して規定電圧値V1に設定された測定用電圧Vmを測定対象体21に出力する電圧出力処理を実行する。

(もっと読む)

半導体装置の故障位置解析方法及び装置

【課題】SiC半導体装置における故障位置をOBIRCH法により解析して特定できるようにした半導体装置の故障位置解析方法及び装置を提供する。

【解決手段】半導体装置の基板の裏面側から、該基板の表面側のデバイス及び回路に、レーザー光を走査しながら照射して加熱すると共に、前記デバイス及び回路に電流を流し、電流の変化によって抵抗値変化を検出して、故障位置を解析する半導体装置の故障位置解析方法において、前記半導体装置が、NドープSiC基板を用いた半導体装置であり、前記レーザー光として、波長650〜810nmのレーザー光を用いる。

(もっと読む)

回路基板検査装置および回路基板検査方法

【課題】検査効率を向上させる。

【解決手段】導体パターンを有する基板に電子部品が搭載された回路基板100における複数の接触点に対してプロービングされたプローブ21を介して入出力する電気信号Sに基づいて電子部品の良否を判定する検査処理を実行すると共に、検査処理において電子部品が不良と判定したときにはプロービングの再実行後に検査処理を再実行する制御部18を備え、制御部18は、検査処理を再実行する際に、直前の検査処理において不良と判定したときの不良の内容が予め決められた特定の内容に該当する電子部品だけを対象として電子部品の良否を判定する。

(もっと読む)

マルチチップ積層体の製造方法

【課題】 本発明の目的は、無基板チップ積層体の導通検査を従来の検査装置で実施可能なTSV実装プロセスを用いて製造するマルチチップ積層体の製造方法を提供する。

【解決手段】 ウエハを分割して形成したチップ110の表面に複数のテスト電極130と複数の外部電極131とを形成する。チップ110には外部電極131とテスト電極130とを導通する複数のシリコン貫通孔111が設けられる。次に、無基板チップ積層体100を接着テープ252の上に固定し、充填封止体150を接着テープ252上に形成する。次に、ウエハテストトレー260内に接着テープ252を支持するテープキャリア250を固定する。導通検査では、無基板チップ積層体100は接着テープ252に接着されたままウエハ検査装置270内に搭載され、ウエハ検査装置270の複数のプローブ271によって無基板チップ積層体100の導通の良否を判定する。

(もっと読む)

半導体装置の製造方法、測定装置、送出装置、及び、プログラム

【課題】仲介部材を介して被測定装置と測定装置を接続した状態で実行される所定の試験の精度を高める。

【解決手段】コンピュータが、仲介部材を介して測定装置に接続された被測定装置の合否を判定する工程を有する半導体装置の製造方法であって、前記仲介部材の抵抗値を算出する抵抗算出工程S10と、前記被測定装置に試験信号を入力し、その後、前記被測定装置から出力された応答信号を取得する測定工程S20と、抵抗算出工程S10で算出された抵抗値を利用して、測定工程S20で取得された応答信号を補正後、補正後の応答信号と、予め定められた規格値との比較結果に基づいて、当該被測定装置の合否を判定する判定工程S30と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】不良電流パスの選別に要する時間を短縮する。

【解決手段】半導体装置は、それぞれ少なくとも1つの貫通電極を含み、インターフェイスチップ内に第1のノードn1を有する複数の電流パス101Xと、互いに異なる複数の電圧値からなる比較電圧DACOUTを生成する比較電圧生成部102と、複数の電流パス101Xそれぞれの第1のノードn1の電圧TSVCXと、比較電圧DACOUTの上記複数の電圧値それぞれとを比較し、比較の結果を示す比較結果信号CMPXを電流パス101Xごとに出力する比較部103と、比較結果信号CMPXに応じて、複数の電流パス101Xのそれぞれが高抵抗化しているか否かを示す結果信号RESLTXを生成する結果信号生成部104とを備える。

(もっと読む)

コンデンサの実装状態判別装置およびコンデンサの実装状態判別方法

【課題】コンデンサの実装・非実装の判別と共に、非実装のときには非実装のコンデンサが実装されるべき位置を判別する。

【解決手段】導体パターン11,12上の測定点P1,P2間のインピーダンスの周波数特性を測定する測定部2と、コンデンサ21〜23が正常に実装された状態での周波数特性に現れる各共振周波数f1〜f3毎に、共振周波数f1〜f3を含む判定範囲fr1〜fr3と共振周波数f1〜f3に対応するコンデンサ21,22,23とを対応付ける基準データD2が記憶された記憶部3と、コンデンサ21〜23の実装状態が未知の導体パターン11,12についての周波数特性を測定部2に測定させ、この周波数特性に現れている共振周波数と基準データD2の各判定範囲fr1〜fr3とを比較して、共振周波数を含まない判定範囲fr1〜fr3に対応付けられたコンデンサが非実装状態であると判別する処理部4とを備えている。

(もっと読む)

データ作成装置、基板検査装置およびデータ作成方法

【課題】部品実装基板に対して行う電気的検査において用いる検査用データを作成する際の入力作業を効率よくかつ正確に行う。

【解決手段】回路基板に電気部品(抵抗器R1,R2,R6,R7)が実装された部品実装基板に対して行う電気的検査において電気信号の入出力を行うための部品実装基板における検査ポイントを示すポイント情報を含む検査用データを作成する処理部と、ポイント情報を入力する操作が可能な操作部と、ポイント情報の入力時に参照させる図であって回路基板の配線(W1〜W3,W6,W7)および電気部品の配置を示す配置図Fを表示部12に表示させる表示制御部とを備え、操作部は、配置図F内に図示されている配線を選択する選択操作が可能に構成され、処理部は、選択操作によって選択された配線を示す情報をポイント情報として検査用データを作成する。

(もっと読む)

データ作成装置、基板検査装置およびデータ作成方法

【課題】検査ポイントや判定用の基準値を正確かつ効率的に設定する。

【解決手段】回路基板に電気部品が実装された部品実装基板に対して行う電気的検査において電気信号の入出力を行うための部品実装基板における検査ポイントを示すポイント情報を含む検査用データを作成可能に構成され、検査用データの作成時に参照させる図であって回路基板の配線および電気部品の配置を示す配置図F2を表示部12に表示させる表示制御部を備え、表示制御部は、配置図F2を表示させる際に、予め設定された条件を満たす電気部品の図示を省略して表示させる第1表示処理を実行可能に構成されている。

(もっと読む)

データ作成装置、基板検査装置およびデータ作成方法

【課題】部品実装基板に対して行う電気的検査において用いる検査用データを作成する際の入力作業の効率を向上させる。

【解決手段】回路基板に電気部品(抵抗器R1〜R8)が実装された部品実装基板における基板の配線(W1〜W7)上に規定されている規定ポイント(P1a〜P7b)の中から選択されて部品実装基板に対して行う電気的検査において電気信号の入出力を行うための検査ポイントを示すポイント情報を含む検査用データを作成する処理部と、配線および電気部品の配置を示す第1配置図を表示部12に表示させる表示制御部とを備え、表示制御部は、第1配置図内に図示されている配線を選択する第1選択操作が行われたときに規定ポイントの配置を示す第2配置図Fbを表示部12に表示させ、その際に、第1選択操作によって選択された配線上に規定されている規定ポイントを他の規定ポイントと識別可能に図示させる。

(もっと読む)

回路基板検査装置

【課題】X−Y型回路基板検査装置で4端子対法による測定を行うにあたって、各可動アームを自由に動き得るようにする。

【解決手段】4端子対法による計測を行うため、電流プローブP1,P2および電圧プローブP3,P4の測定部に至る電気配線に同軸ケーブルC1〜C4を用いるとともに、所定の導体100に接触して互いに導通する第5,第6のプローブP5,P6をさらに備え、第1可動アーム32側に第1電流プローブP1,第1電圧プローブP3および第5プローブP5を設けて、これらの各プローブP1,P3,P5をリード線5を介して接続し、第2可動アーム31側に第2電流プローブP2,第2電圧プローブP4および第6プローブP6を設けて、これらの各プローブP2,P4,P6をリード線5を介して接続する。

(もっと読む)

プローバ装置及びプローブ測定方法

【課題】プローブピンと測定対象物との導通状態を確保しつつ、測定対象物の過度の損傷を抑制することを課題とする。

【解決手段】プローバ装置は、プローブピンと、このプローブピンの先端部を接触させる電極パッドが設けられた半導体ウェハ等の測定対象物が設置される台座部を備える。さらに、プローバ装置は、プローブピンと測定対象物の少なくとも一方を往復振動させる振動発生部を備える。そして、プローブピンの先端部が台座部に設置された測定対象物に接触したときのプローブピンと電極パッドとの間の電気抵抗値Rを取得する検出回路部を備える。制御部は、検出回路部により取得された電気抵抗値Rに基づいて、この電気抵抗値Rが予め設定されたしきい値を越え、導通状態となったか否かを判断する。そして、導通が確保されたら、振動発生部による往復振動を停止させ、測定機器による測定を行う。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム。

【課題】内部信号線の寄生抵抗値を測定できるようにする。

【解決手段】インターフェースチップとコアチップとを電気的に接続する1又は複数の内部信号線101を備え、インターフェースチップは、内部配線に電流を出力する第1の回路111を有し、コアチップは、第1の内部信号線101に電流を出力する第2の回路121を有し、インターフェースチップは、第1の回路111が出力する電流が流れる上記内部配線に接続される第1の入力端子151aと、第1の内部信号線101のインターフェースチップ内の端部101aに接続される第2の入力端子151bとを有し、第1の入力端子151aの電圧と第2の入力端子151bの電圧との電位差に応じた電圧を出力する判定回路150を有する。

(もっと読む)

プロービング装置、検査装置および接続切替え方法

【課題】製造コストの低減を図りつつ、電気的パラメータを正確に測定させる。

【解決手段】電気的パラメータを測定する測定点(測定点Pa1〜Pa10のいずれか)にプロービングさせたプローブ(プローブPb1〜Pb10のいずれか)に対して付与されている第1の識別番号を測定手順データD1に基づいて特定し、かつ特定した第1の識別番号のプローブが接続されているプローブ接続部(接続部C1〜C10のいずれか)の第2の識別番号を、各プローブ接続部に対する各プローブの接続関係に応じて第1の識別番号および第2の識別番号を相互に対応付けた識別番号データD2に基づいて特定し、スキャナ4を制御して、特定した第2の識別番号のプローブ接続部に接続されているプローブを測定部5に接続させる。

(もっと読む)

平面回路基板の電気検査装置及び電気検査方法

【課題】平面回路基板の種類によらず同一装置により検査を行うこと。

【解決手段】電気検査装置2は、平面回路基板1に対向可能に配置され、所定の規則により一様に配列された多数のプローブピン3と、多数のプローブピン3を支持すると共に、多数のプローブピン3を平面回路基板1に対して移動させるためのピンボード4と、各プローブピン3に接続され、各プローブピン3からの信号に基づき平面回路基板1の電気的特性を計測するための計測部12等と、各プローブピン3を、計測部12等に対して選択的に接続するための接続切替部15と、電源部13と、通信部14と、制御部11とを備える。平面回路基板1上に形成されたプローブピン3と接触可能な検査点37A〜37Hの配置は、多数のプローブピン3の配列に整合するように予め配置される。

(もっと読む)

回路基板検査装置

【課題】X−Y型(もしくはフライング型等)の回路基板検査装置おいて、4端子対法による測定を可能とする。

【解決手段】測定部20の測定電流径路に含まれる電流プローブP1,P2および電圧検出径路に含まれる電圧プローブP3,P4と、各プローブを任意方向に移動させる可動アーム31,32と、可動アーム31,32の動きを制御する制御部10とを備え、可動アーム32側で電流プローブP1,電圧プローブP3を支持し、可動アーム31側で電流プローブP2,電圧プローブP4を支持し、電流プローブP1,P2および電圧プローブP3,P4の電気配線に同軸ケーブルC1〜C4を用い、4端子対法とするため、各同軸ケーブルの外部導体Sのすべてをリード線5により接続し、制御部10にて、可動アーム31,32の間隔を常にそれらの間に掛け渡されているリード線5aの配線長の範囲内として、可動アーム31,32の移動を制御する。

(もっと読む)

半導体集積回路のテスト回路及びテスト方法

【課題】同一電源に接続された複数の出力バッファのトランジスタの抵抗値を一括して測定することができる半導体集積回路のテスト回路及びテスト方法を提供すること。

【解決手段】本発明は、出力バッファB1〜Bn及び選択回路SEL1〜SELnを有する。出力バッファB1〜Bnは、電源電圧VDDと出力端子O1〜Onとの間に接続されたPchトランジスタMp1〜Mpnと、グランド電圧GNDと出力端子O1〜Onとの間に接続されたNchトランジスタMn1〜Mnnと、を有する。選択回路SEL1〜SELnは、それぞれ出力バッファB1〜Bnと接続される。選択回路SEL1〜SELnは、それぞれPchトランジスタMp1〜Mpnを非線形領域で動作させた状態において、NchトランジスタMn1〜Mnnをオフにし、又は線形領域で動作させる。

(もっと読む)

半導体集積回路及び半導体装置の試験方法

【課題】半導体集積回路、半導体装置の製造方法、及び半導体装置の試験方法において、電気的な試験の信頼性を高めること。

【解決手段】信号電流I3、I6の入力又は出力に供する内部回路21と、信号電流I3、I6に応じた複製電流I5、I7を出力するカレントミラー部22と、複製電流I5、I7を取り出す試験パッド32とを有する半導体集積回路20による。

(もっと読む)

コンタクトプローブ、プローブ装置、測定装置および検査装置

【課題】測定時間の短縮、回路構成の簡素化、および動作不良発生を低減し、プロービング対象体に対して確実に接続させる。

【解決手段】プローブピン21と、螺旋状溝44を有してプローブピン21に配設された柱状体22と、柱状体22を挿通させた状態で移動可能な筒状体23と、筒状体23の基端部51側に配設されて螺旋状溝44に絶縁状態で係合して筒状体23の移動に伴って柱状体22を回転させる向きに螺旋状溝44を押圧する非導電性ボール24aと、基準電位に接続されると共に筒状体23の先端部52側に配設されて筒状体23が柱状体22の基端部41側に位置しているときに螺旋状溝44に電気的接続状態で係合し、筒状体23が柱状体22の先端部42側に位置しているときに螺旋状溝44から離反する導電性ボール24bと、プローブピン21の先端部32側を筒状体23からの離反方向に付勢するスプリング26とを備えている。

(もっと読む)

1 - 20 / 95

[ Back to top ]