Fターム[2G132AD10]の内容

Fターム[2G132AD10]に分類される特許

1 - 20 / 101

電子回路

【課題】高い精度で所定の検査を行うことができる電子回路を提供する。

【解決手段】本実施の形態に係る電子回路1は、図1(a)に示すように、主に、主回路2への電圧Vccの供給を切り替えるスイッチ素子としてのp型トランジスタ3と、p型トランジスタ3を駆動する第1の駆動信号を出力する駆動部4と、入力側が駆動部4に電気的に接続され、出力側がp型トランジスタ3に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて第2の駆動信号を出力する第1のインバータ部5と、入力側が駆動部4に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて検査のための検査信号を出力する第2のインバータ部6と、第2のインバータ部6の出力側に電気的に接続され、検査信号を出力する第1のパッドとしての検査パッド7と、を備えて概略構成されている。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

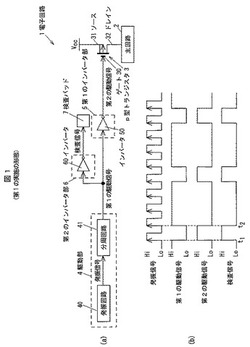

画像表示装置

【課題】画像表示装置において、テスト画像を表示させるための画素駆動信号の出力波形をテストパッドを介して取り出せるようにする。

【解決手段】画像表示装置の水平走査用(ソース駆動用)の画素駆動部4は、画素駆動信号を出力するソースドライバICチップ31、ソースドライバICチップ31から出力される画素駆動信号をディスプレイの画素に供給する出力ライン32、及びテストパッド33がフィルム34上に設けられたチップオンフィルム組立体である。テストパッド33−1、33−2、33−3、33−4は、出力ライン32−1、32−4、32−681、32−684に設けられている。出力ライン32−1〜32−3は、ディスプレイの画素に接続されず、出力ライン32−4〜32−684は、ディスプレイの第1〜第681列目の画素列の各画素に接続される。テスト画像として、ディスプレイの最端の画素列を発光させることによる画像を表示する。

(もっと読む)

電子装置

【課題】電力損失を最小限にすることが可能な複数の電源を含む電子装置を提供する。

【解決手段】パワーアンプ40は、入力電圧Viに基づいた出力電圧の電力を被試験体DUTに供給する。検出回路43は、パワーアンプ40の動作電源であるスイッチング電源22から、パワーアンプ40に電流が流れたことを検出する。選択回路51は、電流が流れない場合には、スイッチング電源22の電圧値を所定値に設定し、電流が流れた場合には、スイッチング電源22の電圧値を入力電圧Viより予め定められた値αだけ大きい値に設定する。

(もっと読む)

プロービング装置

【課題】多点波形測定を必要とする電子部品の電気特性試験において、安価な構成で、かつ簡易な制御によって、被測定物測定点間が狭ピッチであっても、問題なく自動的にプロービングが可能なプロービング装置を得ること。

【解決手段】支持構造体5に垂直固定支持させた多数の両端コンタクトプローブ3の下方端を被測定物1が有する多数の被測定物測定点2に接触設定し、上方端を測定用回路基板8のS面パッド9に接触設定しておく。測定用回路基板8のY軸方向両端におけるC面信号パッド10a、10b及びC面GNDパッド11a,11bはX軸方向に所定数設けてありそれらをプロービングするプローブ12a,12b及びコンタクトプローブ13a,13bをX軸とZ軸の2軸のうちの少なくともZ軸方向に移動制御する。測定用回路基板8は、任意のS面パッド9に伝達された測定点の電気信号を表面信号パッドに伝達できる回路構成になっている。

(もっと読む)

信号発生装置および試験装置

【課題】エッジの位相を固定して、信号のデューティ比を変更する。

【解決手段】指定されたデューティ比の出力信号を出力する信号発生装置であって、入力信号と出力信号との位相差を検出する位相検出器と、位相検出器により検出された位相差をフィルタリングして、発振器に供給するループフィルタと、位相差に応じた周波数の発振信号を出力する発振器と、指定値に応じて発振信号のデューティ比を変更して出力信号として出力するとともに位相検出器に供給するデューティ変更部と、を備える信号発生装置を提供する。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

プリント基板劣化検査装置および劣化検査方法

【課題】プリント基板を破壊することなく、故障発生前にプリント基板またはプリント基板上の回路(検査部位)の修理もしくは交換を容易にできる劣化検査装置を提供する。

【解決手段】プリント基板劣化検査装置は、パルス波を出力するパルス発生器51と、プローブ32と、オシロスコープ53と、コンピュータ60とを備える。プローブ32は、検査部位と接続されたプリント基板上の配線パターンにパルス波を印加するために用いられる。オシロスコープ53は、パルス波がプリント基板から反射された反射波を、プローブ32を介して測定する。コンピュータ60は、プリント基板または検査部位に対して測定された反射波と比較のための参照用波形に基づいて、プリント基板あるいは検査部位の劣化を判定する。

(もっと読む)

検査装置

【課題】クロック信号発生手段の不具合の有無を一目で認識することができる検査装置を提供する。

【解決手段】検査基板400のFPGA92は、入力されたクロック信号の周波数、周期、Duty比の各期待値、実施回数をレジスタ部923へ記憶する(S14)。FPGA92は、入力されたクロック信号CLK1,CLK2の周波数、周期、Duty比を算出する(S32)。FPGA92は、算出したクロック信号CLK1,CLK2の周波数、周期、Duty比のそれぞれがレジスタ部923のクロック信号CLK1,CLK2の周波数、周期、Duty比の各期待値を満たすか否か判定して(S33)、判定結果をレジスタ部923の所定の領域へ記憶する(S34)。FPGA92は、満たさなければ(S35:No)、表示部93のLEDを赤色発光させ(S36)、満たせば(S35:Yes)、LEDを青色発光させる(S38)。

(もっと読む)

半導体装置

【課題】RFチップ本来の回路特性を抽出できるようにする。

【解決手段】半導体試験装置より出力された変調信号を増幅して出力する低雑音増幅器より出力される信号が供給されるとともに、低雑音増幅器により増幅された後に直交復調処理された変調信号を半導体試験装置用基板の伝送路に対して出力する増幅器に入力される信号が供給される試験回路をRFチップに備える。試験回路は、半導体試験装置より出力する変調信号の波形データが予め記憶され、低雑音増幅器より出力される信号及び増幅器に入力される信号をスペクトラム解析した解析結果と記憶されている変調信号の波形データとの比較によりRFチップにおけるチップ内ノイズ及びRFチップ本来の回路特性を抽出する。

(もっと読む)

測定装置、測定方法、試験装置およびプログラム

【課題】被測定信号を効率よく測定する。

【解決手段】予め定められたサイクルで波形パターンが繰り返される被測定信号を測定する測定装置であって、被測定信号をコヒーレントサンプリングするサンプリング部と、サンプリング部が取得したサンプリングデータのうち、波形パターンの一部の区間に対応するサンプリングデータを、予め定められた順番で配列することで、波形パターンのうち、一部の区間に対応する部分波形だけを再構成する波形再構成部とを備える測定装置を提供する。

(もっと読む)

テストシステムおよび半導体装置の製造方法

【課題】様々なノイズのパターンを半導体装置に印加してノイズテストを行うことにより、効率よく、高精度にノイズ耐性の低い半導体装置を出荷前に選別する。

【解決手段】半導体試験装置2は、出力端子PIN3から制御信号を出力してスイッチ5をONとし、静電容量素子7が半導体装置DUTの電源端子に接続された状態にするとともに、出力端子PIN1からノイズ用電圧を出力する。続いて、半導体試験装置2が半導体装置DUTに電源投入するタイミングと略同時に、出力端子PIN2から制御信号を出力してスイッチ6をONさせ、ノイズ用電圧を静電容量素子7に印加し、このノイズ用電圧の電圧立ち上がり時の過渡電流が静電容量素子7に流れ込んでスパイク状のノイズが発生し、半導体装置DUTの電源端子にノイズが印加される。半導体装置DUTにノイズが印加された後、半導体試験装置2は、半導体装置DUTが正常に動作しているか否かを確認する。

(もっと読む)

プローブ装置およびこれを用いた信号測定装置

【課題】プローブ装置−測定部間の高い絶縁性による安全性と、広い周波数帯域に渡って同相信号除去比を確保するための低い対接地容量を確保しつつ、連続動作時間の制約を受けない、または連続動作時間を延ばしたプローブ装置およびこれを用いた信号測定装置を実現する。

【解決手段】入力信号が変調された変調信号を光信号に変換して出力するプローブ装置において、外部から入射される入射光を変調信号に応じて光変調し出射光として出射する光変調部を備える。

(もっと読む)

システムLSIにおける電気信号特性の観測及び解析装置

【課題】システムLSI内部の信号を観測するために、小数個のテストコネクションポイントを設け、そこに選択的に切り替えられた観測対象信号を出力することは出来るが、これでは内部状態を物理的に外部に引き出しただけであり、電気信号単体での波形立ち上がり時間/ジッタ値/アイ・ダイアグラムの開口、また2つ以上の電気信号での位相ズレ、そして観測信号そのものの信号品質について対応が不十分である。

【解決手段】本発明では、内蔵された信号を外部に引き出す場合の特殊な構造を設けることによって、システムLSIにおける電気信号特性の観測及び解析を可能とする。パッケージ上に内蔵された電気信号をデジタル的かつアナログ的に観測することでシステムLSIの解析をするこが可能となる。さらに観測用端子についても最小限に抑えることができ、システムの省スペース化及び、コストダウンに対応することが可能となる。

(もっと読む)

半導体試験装置

【課題】ピンの有効利用形態をとる場合でも、クロストークの少ない良好な試験が可能な、汎用性の高い半導体試験装置を実現する。

【解決手段】被測定デバイス(DUT)への信号印加及び前記DUTから発生される信号の計測を実行するピンエレクトロニクスカードと、前記DUTのピン端子に接触するデバイスボードまたはプローブカードと、前記ピンエレクトロニクスカードの測定ピンを前記DUTの所望のピン端子に対応させるための配線変換部と、この配線変換部と前記デバイスボードまたはプローブカードとをコネクタ接続する勘合部とを具備する半導体試験装置において、

前記ピンエレクトロニクスカードの測定ピンから前記DUTのピン端子との間に、帯域制限回路を挿入した。

(もっと読む)

半導体集積回路および動作試験方法

【課題】半導体集積回路の動作試験における作業者の作業負担の軽減化および作業時間の短縮化を図ること。

【解決手段】半導体集積回路100のCPU101は、リセット制御回路106からリセット信号RSTを受け付ける。CPU101は、電源からの電力の供給が遮断されると記憶内容が消去される第2の記憶部104の記憶内容に基づいて、リセット信号RSTがパワーオンリセット信号PRSTか否かを判定する。CPU101は、判定された判定結果に基づいて、第1の記憶部103に記憶されている複数の動作条件の中から、試験対象回路102を動作させるための動作条件を選択する。CPU101は、選択された動作条件で試験対象回路102を動作させる。

(もっと読む)

半導体装置の試験方法

【課題】半田接続することなく波形測定が可能な半導体装置の試験方法を提供する。

【解決手段】半導体装置Wと接続されたコンタクトリング40の接点41と、パフォーマンスボード31の端子とが対向接続した状態で半導体装置の試験を行う半導体試験装置を用いた半導体装置の試験方法であって、

前記コンタクトリングよりも外側にはみ出した外側領域92と、前記コンタクトリングの前記接点と対向する第1の端子93及び前記パフォーマンスボードの前記端子と対向する第2の端子94を各々両面に有し、前記第1の端子及び前記第2の端子に接続された測定用端子96を前記外側領域内に有する測定用基板90を用意する工程と、

該測定用基板を、前記コンタクトリングと前記パフォーマンスボードとの間に挟んで配置し、前記測定用端子を用いて前記半導体装置の測定試験を行う工程と、を含む。

(もっと読む)

ICテスタ

【課題】ICテスタにおいて、オーバーレンジすることなく高精度レンジで波形測定を行なえるようにする。

【解決手段】多階調電圧を出力するICを試験するICテスタであって、ICの出力電圧から減算するオフセット電圧を発生するオフセット電圧発生器と、オフセット電圧が減算された出力電圧をディジタイズして得られた値を測定データとするA/D変換器と、ICにテストパターンを出力して得られた測定データに基づく測定値を格納する試験を、オフセット電圧を変化させて複数回行ない、オーバーレンジおよびアンダーレンジが発生していない測定値を抽出する高精度波形測定制御部とを備えたICテスタ。

(もっと読む)

半導体装置及びパルス幅検出方法

【課題】半導体装置内部で発生するパルス信号のパルス幅を精度高く簡単に検出する。

【解決手段】ICチップ20に設けられた内部パルス波形変換回路11は、第1のイネーブル信号PLS_RISE_ENが有効で第2のイネーブル信号PLS_FALL_ENBが無効な期間において内部パルス信号PLSが立ち上がるタイミングで予め定められた方向に変化し且つ該変化した後はその状態が予め定められた時間以上継続する内部パルスモニター信号PLSMONを生成すると共に、第1イネーブル信号PLS_RISE_ENが無効で第2イネーブル信号PLS_FALL_ENBが有効な期間において内部パルス信号PLSが立ち下がるタイミングで上記予め定められた方向に変化し且つ該変化した後はその状態が前記予め定められた時間以上継続する内部パルスモニター信号PLSMONを生成する。生成された内部パルスモニター信号PLSMONは、内部パルス信号PLSのパルス幅を検出するテスタ22に対して出力される。

(もっと読む)

半導体パッケージ、半導体装置及び観測信号生成方法

【課題】実装基板上にモニタポイントを配置することなく、適切な位置で信号を観測することができる半導体パッケージ、半導体装置及び観測信号生成方法を提供すること

【解決手段】本発明にかかる半導体パッケージ71は、半導体装置1に実装され、当該半導体装置1に実装された他の半導体パッケージ72から伝送路73を介して入力された入力信号に応じた処理を実行する半導体パッケージ71であって、入力信号に応じた処理を実行する処理回路710と、処理回路710の前段から入力信号を取得し、取得した入力信号を、当該入力信号を観測するテスト信号として半導体装置7の外部に対して出力する転送回路711とを備える。

(もっと読む)

1 - 20 / 101

[ Back to top ]