Fターム[2G132AL05]の内容

Fターム[2G132AL05]に分類される特許

1 - 20 / 295

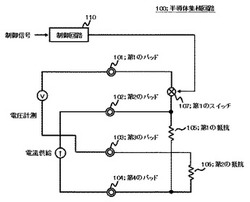

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体装置およびその検査方法

【課題】ウエハ検査時に必要なプローブピンを削減可能にした半導体装置を提供する。

【解決手段】第1のデータを記憶する記憶素子と、データ読み出しの指示が入力されると、記憶素子から第1のデータを読み出して出力するデータ入出力制御部と、データ入出力制御部から出力される第1のデータを第1の端子に出力し、第1のデータを第1の端子に出力するとき、自装置の第2の端子と他の半導体装置の第1の端子とを接続するプローブカードを介して他の半導体装置から受信する第2のデータを保持し、その後、第2のデータを自装置の第1の端子に出力するデータラッチ部とを有する。

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

半導体集積回路のテスト回路及びテスト方法

【課題】外部端子数の増加を抑えつつ、半導体集積回路のテスト時間を短縮する。

【解決手段】テスト回路は、入力されるリファレンスクロック109を逓倍して、テスト対象回路106をテスト動作させるための実動作クロック112及びサンプリングクロック105を生成するPLL108と、入力されるテストコマンドに従い、テスタ同期クロック103に同期してテスト対象回路106のテスト結果を出力するテスト結果出力回路107と、を備えるテスト回路であって、テストコマンドを含むテスト入力信号104とサンプリングクロック105とに基づきテスタ同期クロック103を生成するテスタ同期クロック生成回路100を備えるものである。

(もっと読む)

温度検出回路

【課題】 消費電流を抑えるため間欠動作するようにした温度検出用半導体集積回路において、外部端子を増加させることなく回路の評価および検査が行えるようにする。

【解決手段】 発振回路(16)を備え、消費電流を抑えるため間欠動作する温度検出用半導体集積回路において、温度検出回路(11)の出力と基準電圧とを比較する電圧比較回路(13)の出力に対応した信号を出力する外部端子(DET)と、該外部端子に負電位が印加されたことを検出した場合に、温度検出回路と基準電圧回路と電圧比較回路を活性化させる信号を生成する制御回路(17)と、制御回路が活性化信号を出力しかつ温度検出回路の出力が基準電圧を超えたと電圧比較回路(13)が判定した場合に電流を流す電流回路(SW1,R0,SW2)とを設けるようにした。

(もっと読む)

評価基板

【課題】評価環境を簡易化し、評価の効率化を図ることができる評価基板を得る。

【解決手段】評価基板1はパワーモジュール2を評価するために用いられる。パワーモジュール2は、パワー半導体装置3と、パワー半導体装置3の特性を検出する温度検出部4及び電圧検出部5とを有する。評価基板1の1枚の基板7に、電源回路8、フォトカプラ駆動回路9、及び表示部10が設けられている。電源回路8はパワーモジュール2に電力を供給する。フォトカプラ駆動回路9はパワー半導体装置3を駆動する。表示部10は温度検出部4及び電圧検出部5から入力した検出信号を表示する。

(もっと読む)

最適化されたJTAGインターフェイス

【課題】

集積回路内のJTAGタップドメインにアクセスするのに最適化されたJTAGインターフェイスが使用される。限定はしないが、シリアル通信関連集積回路テスト、エミュレーション、デバッグ、および/またはトレース操作等の多様なシリアル通信操作に対してインターフェイスを使用することができる。

【解決手段】

TDI入力端子、TCK入力端子、TMS入力端子、およびTDO出力端子を有し、TDO出力端子は集積回路の外部アクセス可能なデータ入出力ピンに接続されているIEEE 1149.1タップドメインと、集積回路の外部アクセス可能なデータ入出力ピンに接続されたシリアル入力端子、TDI入力端子に接続された第1のパラレル出力端子、およびTMS入力端子に接続された第2のパラレル出力端子を有するシリアル入力パラレル出力回路とを含む、集積回路。

(もっと読む)

半導体集積回路及びその設計方法

【課題】半導体集積回路の外部端子としてTRSTがなくても、論理シミュレーションの際に、タップコントローラのステートを確定する。

【解決手段】タップコントローラ2は、リセット端子(端子p4)を有し、回路部3は、タップコントローラ2における状態遷移を制御するステート制御信号と、クロック信号を入力し、ステート制御信号とクロック信号に応じて、リセット端子p4にリセット信号を供給することで、タップコントローラ2のステートを確定する。

(もっと読む)

半導体集積回路装置のテスト方法およびテストボード

【課題】半導体集積回路装置の入力端子数よりも少ない端子数のテスタを用いて半導体集積回路装置のテストを行うテスト方法を提供すること。

【解決手段】半導体集積回路装置のテスト方法は、半導体集積回路装置の複数の入力端子とテスタからのテスト信号を受信するテスタ端子とを、多対1に電気的に接続するテストボードを介して、該テスタから該半導体集積回路装置に所定のテストパタン信号を送信する工程と、前記半導体集積回路装置の出力端子から出力された出力信号と、前記所定のテストパタン信号に対応する期待値とを比較して、前記半導体集積回路装置の良否を判定する工程と、を含む。

(もっと読む)

表示装置の駆動回路及びそのテスト制御方法

【課題】テスト時に使用するプローブ数が増加する。

【解決手段】表示装置の第1、第2のデータ線をそれぞれ駆動する表示装置駆動回路であって、前記表示装置に表示する第1、第2の表示データとをそれぞれ格納し、第1、第2の信号とをそれぞれ出力する第1、第2のデータレジスタと、前記第1、第2の信号に応じて、第1、第2のアナログ信号をそれぞれ出力する第1、第2のDAコンバータと、前記第1、第2のアナログ信号とに応じて、前記第1、第2のデータ線を駆動する出力端子対と、テスト時に、外部テスト回路からのテスト制御信号に応じて、前記出力端子対の一方に対して、前記第1の表示データに基づく第1のテスト出力と前記第2の表示データに基づく第2のテスト出力とを選択的に出力するスイッチ回路と、前記スイッチ回路を制御する制御回路と、を有する表示装置駆動回路。

(もっと読む)

完全に不定値許容性であって非常に高スキャン圧縮なスキャンテストシステム及び技術

【課題】完全に不定値許容性の非常に高スキャン圧縮なスキャンテストシステム及び技術を提供する。

【解決手段】スキャンテスト及びスキャン圧縮は、コストの低減及び高い出荷品品質を実現するうえで重要である。従来以上に複雑な設計における新しいタイプの故障には、高い圧縮が必要とされる。しかしながら、不定値(X)の密度が増加し効果的な圧縮を妨げる。スキャン圧縮の方法では、任意の密度の不定値について非常に高い圧縮及び完全な検出率が達成される。記載された技術は、テスト容易化設計(DFT)及び自動テストパターン生成(ATPG)のフローに完全に組込むことができる。産業的な設計にこれらの技術を用いた結果、他の方法と比べて一定かつ予測可能な有利な点があることが分かった。

(もっと読む)

半導体装置及びその検査方法

【課題】 テスタの高機能化や多ピン化、及び、テスト処理能力の低下を招くことなく、液晶ドライバが生成する階調電圧値の検査を行うことができる半導体装置、及びその検査方法を提供する。

【解決手段】

被テストデバイスである半導体装置30は、液晶ドライバ20のほか、テスト制御回路31、階調ばらつき判定回路33、及び、出力切替スイッチ34を備え、被テストデバイスである半導体装置30自身が、テスト用制御信号、及び、テスト用クロック信号に基づき、テスト用の階調電圧を生成するとともに、生成した階調電圧値が外部の半導体試験装置(テスタ)32から供給される基準電圧値に対してばらつきが許容範囲に収まっているか否かを階調ばらつき判定回路33が判定し、その判定結果を半導体試験装置32に出力する。

(もっと読む)

集積回路装置および集積回路装置の試験方法

【課題】メモリへの連続アクセス回数を増やしても使用するスキャンチェーン数を増加させることなく試験を行うことができる集積回路装置の提供を図る。

【解決手段】メモリMEMと、該メモリに接続される複数のロジック回路Lと、前記メモリおよび前記ロジック回路の試験を行うスキャンチェーンSCI,SCIIと、を含む集積回路装置であって、前記メモリの前段の第1スキャンチェーンSCIにおいて、前記メモリに対して出力端子が繋がっている少なくとも2つの第1および第2フリップフロップFF107,FF108を有し、前記第2フリップフロップFF108の前記出力端子と、前記第1フリップフロップFF107のスキャン入力端子の間に、少なくとも1つの第1挿入フリップフロップFF105,FF101を挿入して、前記スキャンチェーンの接続を規定する。

(もっと読む)

半導体装置

【課題】 電源遮断機能を有する半導体装置において試験用パッドを設けることなく電源ショート試験の実施を可能にする。

【解決手段】 半導体装置は、回路ブロックと、第1電源線と回路ブロックに電源電圧を供給する第2電源線との間に設けられる第1スイッチと、第1電源線と第2電源線との間に設けられる第2スイッチとを備え、第1スイッチは、テストモード時にオンし、第2スイッチは、テストモード時にオフし、第2スイッチのオン/オフに応じて、通常動作モード時に、回路ブロックの動作状態がオン/オフする。

(もっと読む)

故障診断システム、半導体集積回路及び故障診断方法

【課題】固定数の出力端子を用いて、複数の入力信号の中から故障の原因となる信号を特定して故障を診断すること。

【解決手段】第1の入力テスト信号と、当該第1の入力テスト信号の期待値である第1の期待値と、のいずれかを選択して出力する第1の選択回路と、第2の入力テスト信号と、第1の選択回路からの出力信号との一致判定結果を出力端子へ出力する第1の論理回路と、を有する第1の圧縮回路と、第1の選択回路により第1の入力テスト信号が選択された際の出力端子からの第1の出力結果がエラーを示す場合に、第1の選択回路に対して第1の期待値を選択させ、第1の出力結果がエラーを示すことに伴い第1の選択回路により第1の期待値が選択された際の出力端子からの第2の出力結果が正常を示す場合に、第1の入力テスト信号をエラーと特定し、第2の出力結果がエラーを示す場合に、第2の入力テスト信号をエラーと特定する選択制御回路とを備える。

(もっと読む)

半導体装置

【課題】テスト信号毎の専用配線を不要とし、配線領域を削減できるテスト回路を備えた半導体装置を提供する。

【解決手段】外部から供給されるテスト情報をデコーディングし、複数の信号を生成するDFTデコーダ202と、互いに従属接続した複数のDFTレジスタDFTr0〜DFTrnと、複数のDFTレジスタにそれぞれ対応する複数の制御回路(制御回路CKT0〜CKTn)と、複数のレジスタのうちの第1のレジスタ(DFTレジスタDFTr0)に複数の信号(シフトデータTSCANDATA)を供給するセレクタ(セレクタ113)と、セレクタのセレクティング回数を規定するカウンタ(9bitカウンタ112)と、複数の制御回路の数に対応するクロック周期の回数を、複数のレジスタ及びカウンタに供給するシフトクロック生成回路(シフトCK制御回路111)と、を備える。

(もっと読む)

テストモード設定回路

【課題】端子数の少ないテストモード設定回路を提供する。

【解決手段】半導体装置のテストモードを制御するテスト端子に、低閾値電圧のディテクタと高閾値電圧のディテクタを設け、低閾値電圧のディテクタによって論理回路のリセットを解除し、高閾値電圧のディテクタでテストモードを切替え制御するような構成にした。従って、テスト端子とリセット端子とテストモード制御端子が共通になり、端子の数を大幅に削減することが可能である。

(もっと読む)

テスト回路、及び、シリアルI/F回路、半導体装置

【課題】半導体パッケージにテストモード時にのみ使用される端子を設けなくても、テストモードの設定及びテストモード設定後のテスト信号入力ができるテスト回路を提供する。

【解決手段】複数の電圧レベルを含むパルスパターンを有するテストモード用電圧と基準電圧とを比較して、トリガー信号及びデータ信号を含むパルス信号をそれぞれ出力する複数の比較器6a〜6cと、トリガー信号に基づいてデータ信号をシリアル/パラレル変換してテスト信号を生成し、テスト信号を被テスト回路9に供給するテスト信号生成回路5とによってテスト回路を構成する。

(もっと読む)

1 - 20 / 295

[ Back to top ]