Fターム[2H092JA31]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545) | チャネル長規定 (130)

Fターム[2H092JA31]に分類される特許

61 - 80 / 130

半導体装置およびその作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】酸化物半導体層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、該酸化物絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。また、チャネル保護層に重ならないようにソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層上の絶縁層が酸化物半導体層と接する構成とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層と、ゲート電極層上に設けられるゲート絶縁層と、ゲート絶縁層上に設けられる第1の酸化物半導体層と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置及び電子機器

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイン電極に接触しない。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

表示装置

【課題】D/A変換回路の構成を複雑にすることなく、小型化された表示装置を提供する。

【解決手段】赤のLEDと、緑のLEDと、青のLEDとが順次点灯する期間を有することによりフィールドシーケンシャル駆動が行われ、赤のLEDが点灯する期間、緑のLEDが点灯する期間、及び青のLEDが点灯する期間のそれぞれにおいて、複数のサブフレーム期間を有し、サブフレーム期間に書き込まれたアナログビデオデータの階調電圧の総和を時間平均したものを用いて表示を行う。

(もっと読む)

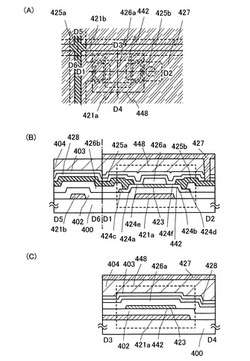

a−SiTFT及びこのa−SiTFTを有するシフトレジスター

【課題】櫛型状の電極を採用してジグザグ状のチャネル領域を形成したa−SiTFTに

おいて、帯状凸部の形成数を抑制してもチャネル幅を長く形成することができ、それによ

り高速駆動が可能で、かつ電極の断線が抑制された信頼性の高いa−SiTFTを提供す

ること。

【解決手段】ソース電極Sを、半導体層a−Siの表面において複数の凹凸部を描きなが

らジグザグに連なる1本の線形状に形成し、ドレイン電極Dを、半導体層a−Siと非重

畳の基幹部DNと、基幹部から分岐されて半導体層a−Siの側端部を乗り超えて半導体

層a−Siの表面に配置されると共に、ソース電極Sの電極の凹部にその先端部が挿入さ

れるように配置された複数の帯状凸部DTと、からなる櫛型状に形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

液晶表示装置

【課題】画面全体でフリッカの発生を抑制し、表示品位の高い液晶表示装置を提供する。

【解決手段】マトリクス状に配置された複数の表示画素PXからなる表示部DYPと、複数の表示画素PXのそれぞれに配置された画素電極PEと、複数の走査線GLと、複数の信号線SLと、複数の表示画素PXのそれぞれにおいて、対応する信号線SLと画素電極PEとの接続を切り替える第1及び第2スイッチング素子SW1、SW2と、を備え、第1及び第2スイッチング素子SW1、SW2は、対応する走査線GLと電気的に接続された第1及び第2ゲート電極GE1、GE2と、第1及び第2ゲート電極GE1、GE2とゲート絶縁膜を介して対向配置された半導体層L1と、を備え、対応する走査線GLに走査電圧が伝達される方向において、第1スイッチング素子SW1の第1ゲート電極GE1と半導体層L1とが対向する領域は大きくなる液晶表示装置である。

(もっと読む)

表示装置

【課題】遮蔽膜とコモン線とを接続しないで良質な画像表示を行うことができるアクティブマトリクス型表示装置を提供する。

【解決手段】複数の画素TFTと、前記画素TFTに電気的に接続された画素電極と、遮蔽膜とが設けられた基板を有するアクティブマトリクス型液晶表示装置であって、遮蔽膜はフローティングになっており、画素電極と前記遮蔽膜との間に第1の誘電体を有し、遮蔽膜と前記コモン線との間に第2の誘電体を有する。

(もっと読む)

液晶表示装置

【課題】従来よりも簡単な構造でマルチ画素構造を実現する。

【解決手段】画素10は第1副画素10aと第2副画素10bとを有する。第1副画素に対応して設けられた第1TFT16Aと、第2副画素に対応して設けられた第2TFT16Bは、共通のゲートバスラインおよび共通のソースバスラインに接続されている。第1TFT16Aのオン電流は第2TFT16Bのオン電流よりも大きい。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と重畳する第1酸化物半導体層と、第1酸化物半導体層のチャネル形成領域と重なる領域を覆うチャネル保護層と、第1酸化物半導体層上においてゲート電極と端部が重畳し、導電層と第2酸化物半導体層が積層された第1配線層及び第2配線層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極を走査線又は信号線と接続し、ゲート電極の電位を印加するための非線形素子の第1配線層又は第2配線層とゲート電極の接続を直接接続することで、接続抵抗の低減による安定動作と接続部分の占有面積の縮小を図る。

(もっと読む)

低分子有機半導体物質を利用する液晶表示装置及びその製造方法

【課題】本発明は、水分に非常に弱い特性を有する低分子有機半導体物質をシャドーマスクを利用しないで数μmまで調節可能な微細パターンで形成することができ、微細パターンされた低分子有機半導体層の損傷なしに低分子有機半導体物質を利用した液晶表示装置用アレイ基板の製造方法を提供する。

【解決手段】本発明では、画素領域と;ゲート電極と、上部面を有するゲート絶縁膜と、ゲート絶縁膜の上部面に形成されたソース電極及びドレイン電極と、ゲート絶縁膜の上部面に配置されて、ソース電極とドレイン電極間でチャネル領域を定義して、低分子有機半導体物質からなった半導体層を含み、基板上に画素領域に隣接するように位置する薄膜トランジスタと;チャネル領域を覆っており、ソース電極とドレイン電極それぞれの上部面と一致したりまたはその下に位置する上部面を有する第1保護膜を含む液晶表示装置を提供することを特徴とする。

(もっと読む)

表示装置

【課題】表示領域の周辺にCMOSTFT用いて駆動回路を形成した表示装置において、CMOSTFTを構成するPMOSTFTの特性を安定化させる。

【解決手段】CMOSTFTにおける右側のPMOSTFTにおいて、N型のチャネル領域8とチャネル幅方向周辺にP型領域7bが形成されている。P型であるソース領域14において、第1のN型領域12bをチャネル領域のP型領域7bに接して形成し、第1のN型領域12bに接してそれよりも不純物密度の大きい第2のN型領域11aを形成する。第1および第2のN型領域とP型であるソース領域14に形成されるPN接合によってチャネル部周辺のP型領域7bを通過する電流を抑制し、PMOSTFTの特性を安定化する。

(もっと読む)

酸化物半導体、薄膜トランジスタ並びに表示装置

【課題】酸化物半導体の組成若しくは欠陥制御をすることを目的の一とし、また、薄膜トランジスタの電界効果移動度を高め、オフ電流を抑えつつ十分なオンオフ比を得ることを他の目的の一とする。

【解決手段】InMO3(ZnO)n(M=Ga、Fe、Ni、Mn、Co及びAlから選ばれた一又は複数の元素、nは1以上50未満の非整数)でありさらに水素を含む。この場合において、Znの濃度がIn及びM(M=Fe、Ga、Ni及びAlから選ばれた一又は複数の元素)よりも低くする。また、当該酸化物半導体はアモルファス構造を有している。ここでnの値は、好ましくは1以上50未満の非整数、より好ましくは10未満の非整数とする。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに、電気光学装置及び電子機器

【課題】例えば、液晶装置において、画素ピッチの微細化に対する要請に応じつつ、当該微細化によって得られるべき表示性能の向上を十分に享受可能な薄膜トランジスタを提供する。

【解決手段】ドレイン領域(1d)の夫々の幅(W1)は、幅方向に沿って、チャネル領域(1c)の幅(W3)より細い。加えて、ドレイン領域(1d)の夫々の厚み(T1)は、チャネル領域(1c)の厚み(T3)より薄い。したがって、TFT(30)のドレイン領域(1d)の側面及び上面からなる表面の面積は、比較例に係るTFTのドレイン領域の表面の面積より小さい。よって、TFT(30)によれば、ゲート電極(3a2)で遮光されないドレイン領域(1d)の夫々の表面積を低減することができ、TFT(30)の上側から3次元的に照射される光のうちドレイン領域(1d)が受ける光量を低減することが可能であり、光リーク電流を低減することができる。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置及びシステム

【課題】高いキャリア移動度とノーマリーオフ特性とを有する電界効果型トランジスタを提供する。

【解決手段】ゲート電圧を印加するためのゲート電極26と、電流を取り出すためのソース電極23及びドレイン電極24と、ソース電極23及びドレイン電極24に隣接して設けられ、マグネシウム(Mg)とインジウム(In)を主成分とする酸化物半導体からなる活性層22と、ゲート電極26と活性層22との間に設けられたゲート絶縁層25とを備えている。そして、活性層22を形成する際に流す酸素ガスの流量は、酸素分圧が1.7×10−3Paとなるように調整されており、活性層22を構成する酸化物半導体は、体積抵抗率が10Ωcmで、酸素が非化学量論組成であるMgIn2O4系酸化物半導体となる。

(もっと読む)

薄膜トランジスタ、および薄膜トランジスタアレイ

【課題】 薄膜トランジスタの特性を良好にすると同時に、蓄積容量部に形成される金属−絶縁体−半導体構造(MIS構造)を解消しキャパシタの値を安定化させることで、フォトマスク工程数を削減しても高い性能を維持できる薄膜トランジスタ及びそれを用いた表示装置を提供する。

【解決手段】 4回以下のフォトマスク工程数で作製される薄膜トランジスタ部216と、蓄積容量部217とを有する薄膜トランジスタアレイ基板において、チャンネルの形成に寄与しない活性半導体層をシリサイド化する。

(もっと読む)

薄膜トランジスタ、及び当該薄膜トランジスタを有する表示装置とその駆動方法

【課題】閾値電圧の制御が可能で、スイッチング特性が良好な薄膜トランジスタを提供する。

【解決手段】第1のゲート電極層と、半導体層と、第1のゲート電極層と半導体層との間に設けられた第1のゲート絶縁層と、半導体層とオーミック接触する層を介して半導体層上に設けられたソース電極及びドレイン電極層と、第1のゲート電極層の一部と重畳して第1のゲート絶縁層と半導体層により覆われた導電層と、少なくとも半導体層のバックチャネル部を覆って設けられた第2のゲート絶縁層と、半導体層のバックチャネル部と重畳する、第2のゲート絶縁層上に第2のゲート電極層と、を有する薄膜トランジスタを提供する。または、導電層は、第1のゲート電極層の一部と重畳して半導体層の下に存在し、且つ前記半導体層よりも移動度の高い半導体により形成されていてもよい。第2のゲート電極層は、所謂バックゲートとして機能する。

(もっと読む)

薄膜トランジスタ及びこれを用いた表示装置

【課題】 ハンプ特性を低減し、回路の低消費電力化等を実現することが可能な薄膜トランジスタ及び表示装置を提供する。

【解決手段】 画素領域と周辺回路領域とを有する表示装置の周辺回路領域に形成される薄膜トランジスタである。チャネルを構成する多結晶シリコン薄膜13のゲート幅方向両端部において、ゲート電極15のゲート長が拡大され突出部15Aが形成されている。薄膜トランジスタのゲート長は2μm以下であり、ゲート幅は10μm以上である。突出部15Aの突出長は2μm以上であり、突出幅は0.5μm以上である。

(もっと読む)

61 - 80 / 130

[ Back to top ]