Fターム[2H092JA31]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545) | チャネル長規定 (130)

Fターム[2H092JA31]に分類される特許

81 - 100 / 130

薄膜トランジスタおよびその製造方法

【課題】 真性酸化亜鉛からなる半導体薄膜を有する薄膜トランジスタの製造に際し、加工精度を良くする。

【解決手段】 まず、真性酸化亜鉛からなる半導体薄膜8の上面全体に保護膜9を形成し、その上に上層絶縁膜12を成膜する。次に、上層絶縁膜12および保護膜9にコンタクトホール10、11を形成する。この場合、チャネル長Lは2つのコンタクトホール10、11間の間隔により決定され、チャネル幅Wはコンタクトホール10、11の所定方向の寸法により決定される。これにより、半導体薄膜8にサイドエッチングがやや生じても、チャネル長Lおよびチャネル幅Wに寸法変化が生じることはない。

(もっと読む)

半導体装置の製造方法

【課題】 特性のばらつきを抑制した半導体素子を備える半導体装置を製造するための製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体層(Se)の第1領域(Sa)と第2領域(Sb)との間の少なくとも一部にスリット(SL)を形成する工程と、第1開口部(Oa)および第2開口部(Ob)の設けられたマスク層(M)を形成する工程と、半導体層(Se)の第1領域(Sa)および第2領域(Sb)に触媒元素(Ct)を導入し、半導体層(Se)の第1領域(Sa)および第2領域(Sb)のそれぞれの結晶化を行う工程と、半導体層(Se)の第1領域(Sa)および第2領域(Sb)をパターニングした第1島状半導体層(122)および第2島状半導体層(142)を用いて半導体素子(120)および半導体素子(140)を作製する工程と包含する。

(もっと読む)

酸化物半導体及びこれを含む薄膜トランジスタ

Zn、In、及びHfを含み、Zn、In、及びHf原子の全体含有量対比Hf原子含有量の組成比が2〜16at%である酸化物半導体及びこれを備える薄膜トランジスタを提供する。 (もっと読む)

半導体装置

【課題】半導体の吸収端波長より長波長の光を半導体に照射する機構と、該光の調節機構とを設置することで、半導体の閾値電圧変化を補償又は抑制することが可能な半導体装置を提供する。

【解決手段】少なくとも半導体を構成要素として有する半導体素子を備えた半導体装置であって、前記半導体の吸収端波長より長波長の光を該半導体に照射する機構と、前記光が通過する光路の一部に設けられた、光の強度、照射時間又は波長から選択される少なくとも1つの要素を調節する調光機構と、を有し、前記調光機構によって調節された前記光により、前記半導体素子の閾値電圧を変化させることを特徴とする。

(もっと読む)

新規な有機半導体材料

【課題】塗工や印刷等の簡便なプロセスで製造できる、チオフェンとフェニレンからなる溶解性に優れた低分子有機半導体材料を提供する。

【解決手段】下記一般式(I)で表されることを特徴とする有機半導体材料。

(一般式(I)中、R1、R2、R3、R4、R5及びR6は、それぞれ独立に、置換もしくは無置換のアルキル基、置換もしくは無置換のアルコキシ基又は置換もしくは無置換のアルキルチオ基又は水素を表わし、R2、R3、R5及びR6の少なくとも一つは、置換もしくは無置換のアルキル基、置換もしくは無置換のアルコキシ基又は置換もしくは無置換のアルキルチオ基であり、nは1〜8の整数を表わす。)

(もっと読む)

液晶表示装置用基板、液晶表示装置及びその製造方法

【課題】静電気の荷電量に関係なしに静電気から液晶表示基板を保護すること。

【解決手段】画像を表示する多数の画素電極と半導体素子とを有している透明な絶縁の第1基板と、前記第1基板上に形成され前記半導体素子と連結された配線と、隣接した前記配線との間に連結され、前記第1基板から発生される静電気を消耗させる多数のスパーク誘導回路とを含む。

(もっと読む)

電気光学装置、電子機器

【課題】貼り合わせにおいて、一方の基板に対して他方の基板の位置ずれが生じたとして

も、他方の基板における遮光膜によって、表示領域における各画素の開口率のばらつきを

低減させ、液晶装置毎に、画素の開口率がばらつくことを防ぐとともに、一方の基板のト

ランジスタを確実に遮光することができる構成を有する電気光学装置を提供する。

【解決手段】対向配置された一対の基板を有する液晶装置であって、TFT基板に、走査

線11aとデータ線6aとがマトリクス状に交差するように形成されているとともに、走

査線11aとデータ線6aとの交差領域80に、TFT30の半導体層1が設けられてお

り、対向基板に、TFT30を遮光する、半導体層1と少なくとも一部が平面視した状態

で重なる島状のBM25が設けられていることを特徴とする。

(もっと読む)

液晶表示装置

【課題】TFT基板と対向基板の間隔をTFT基板に形成した支柱によって規定し、かつ支柱部分からの光漏れをなくする。

【解決手段】ドレイン線107と走査線104の交点にTFT基板と対向基板の間隔を規定する支柱130を形成する。支柱130が形成される交点ではドレイン線107の幅を大きくすることによって光漏れを防止する。また、支柱130が形成される交点では、走査線104の幅を小さくすることによって、ドレイン線107と走査線104間の容量の増加を防止する。また、支柱130は特定の色の画素、例えば青画素Bに対応する交点に形成する。これによって、支柱130を形成したことによる透過率の差および、薄膜トランジスタの特性差を初期的に補償する。

(もっと読む)

液晶表示装置

【課題】本発明は、静電気保護素子を備えた液晶表示装置に関し、冗長性に優れ、比較的低い電圧が長時間発生する静電気に対しても十分な保護機能を備えた液晶表示装置を提供することを目的とする。

【解決手段】静電気保護素子部28、30は、外部取り出し電極16、18に接続されるソース電極(S)と共通線22、24に接続されるドレイン電極(D)とを有する第1のTFT32と第1のTFT32ゲート電極(G)に接続された導電体42と、外部取り出し電極16、18に接続されたソース電極(S)と導電体42に接続されたドレイン電極(D)と電気的に孤立しているゲート電極(G)とを有する第2のTFT38と、共通線22、24に接続されたソース電極(S)と導電体42に接続されたドレイン電極(D)と電気的に孤立しているゲート電極(G)とを有する第3のTFT40とを備えている。

(もっと読む)

薄膜トランジスタ構造、表示装置及びその製造方法

【課題】抵抗制御が容易で、品質の良好な薄膜トランジスタ構造、表示装置及びその製造方法を提供する。

【解決手段】薄膜トランジスタ構造10において、半導体層22は、p型不純物イオンのみドープされたチャネル領域30を備えている。半導体層22は、チャネル領域30を間に挟むと共に、ソース領域35及びドレイン領域36として機能する一対の高濃度不純物領域33を備えている。半導体層22は、ソース領域35とチャネル領域30と、及び、ドレイン領域36とチャネル領域30と、の間にそれぞれ形成されてn型不純物イオンのみドープされた低濃度不純物領域(LDD領域31,32)を備えている。ゲート電極24は、チャネル領域30及びLDD領域31,32をオーバーラップするように形成されている。

(もっと読む)

薄膜トランジスタ

【課題】特性のばらつきを抑制できる薄膜トランジスタを提供する。

【解決手段】ガラス基板2上に設けられエッチングにより形成された端部5を有する多結晶又は非晶質Siからなる半導体層4と、半導体層4の両側に設けられたソース領域8およびドレイン領域9と、ソース領域8およびドレイン領域9間に設けられたチャネル幅が1μm以下のチャネル領域10と、チャネル領域10上にゲート絶縁膜6を介して設けられたゲート電極7と、チャネル領域10のチャネル幅方向のゲート電極7で被覆された端部5に電流が流れないように絶縁化された絶縁膜11とを具備し、ゲート電極7で被覆された端部5がしきい値電圧に寄与しない構造にした。

(もっと読む)

半導体装置の作製方法、半導体装置、及び電子機器

【課題】単結晶半導体層の剥離の発生率を抑えた半導体装置を作製することを課題とする。また、トランジスタの不良発生率を低減した半導体装置を提供することを課題とする。また、回路配置を最適化した小型の半導体装置を提供することを課題とする。

【解決手段】(110)面を主表面に有する単結晶半導体基板において、主表面にイオンを照射して単結晶半導体基板中に脆化層を形成し、単結晶半導体基板の主表面に絶縁層を形成し、絶縁層と、絶縁表面を有する基板とを接合させ、単結晶半導体基板を、脆化層において分離させることにより、絶縁表面を有する基板上に、(110)面を主表面とする単結晶半導体層を形成し、単結晶半導体層の<110>軸方向がチャネル長方向となるように、nチャネル型のトランジスタとpチャネル型のトランジスタを形成する。

(もっと読む)

液晶表示装置及び電子機器

【課題】開口率を向上した液晶表示装置及び電子機器を提供することを課題とする。

【解決手段】絶縁表面を有する基板と、基板上に形成されたトランジスタと、トランジスタに電気的に接続された画素電極と、を有し、トランジスタは、ゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上の微結晶構造を有する半導体層と、微結晶構造を有する半導体層上のバッファー層と、を有し、トランジスタのチャネル幅Wと、トランジスタのチャネル長Lとは、0.1≦W/L≦1.7の関係を満たすことを特徴としている。

(もっと読む)

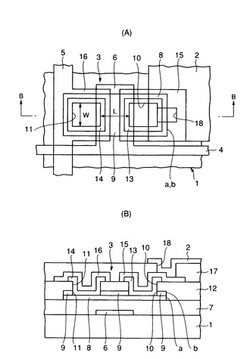

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、例えば周辺回路を構成するトランジスタの特性を向上させる。

【解決手段】電気光学装置は、基板10上に、複数の画素電極9aと、複数の画素電極が配列された画素領域の周辺に位置する周辺領域に設けられ、(i)基板上における第1方向(X方向)に沿ったチャネル長を夫々有すると共に第1方向に交わる第2方向(Y方向)に所定間隔を隔てて並列するように形成された複数のチャネル領域74Cと、複数のチャネル領域に対して共通に夫々電気的に接続されたソース領域74S及びドレイン領域74Dとを有する半導体層74と、(ii)複数のチャネル領域に重なるように第2方向に沿って延在するゲート電極71Gとを有するトランジスタ71とを備える。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタおよび表示装置

【課題】TFTのL長バラツキを抑制する。

【解決手段】絶縁基板1上にゲート電極2、ゲート絶縁膜3および非結晶質シリコン膜4を順に形成する工程と、前記非結晶質シリコン膜4のチャネル領域となる領域上のみにチャネル保護膜を形成する工程とを含み、前記チャネル保護膜を形成する工程では、当該チャネル保護膜がエッチングレートの異なる複数の層5a,5bからなる積層構造を有するとともに、当該積層構造における最下層5aが当該最下層5aを除く他の層5bのエッチングバラツキをリセットするための選択性を持つ膜構成となるように、当該チャネル保護膜を形成する。

(もっと読む)

電子回路、電気光学装置およびこれを備える電子機器

【課題】ポリシリコン薄膜トランジスターにふさわしいA/D変換回路を提供する。

【解決手段】アクティブマトリクス基板101上に薄膜ポリシリコンを能動層に用いたト

ランジスターを備えた電子回路であって、測定量を電流量に変換するセンサー1と、前記

電流量に応じた電圧に変換する電流電圧変換回路(コンデンサー12、コンデンサー14

、トランジスター11、トランジスター15)と、変換された電圧を検出し、所定の信号

を出力する電圧検出回路(コンパレーター回路3)とを備え、前記電圧検出回路は、複数

のCMOSクロックド・インバーター(クロックド・インバーター370、380)で構

成され、前記CMOSクロックド・インバーターを構成するNチャネル型トランジスター

のチャネル幅とPチャネル型トランジスターのチャネル幅の比が異なる。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】酸化物を含むチャネル層を有し、信頼性のある薄膜トランジスタを提供する。

【解決手段】酸化物を含むチャネル層を有する薄膜トランジスタ表示板及びその製造方法に関し、絶縁基板、絶縁基板上に形成され、酸化物を含むチャネル層、チャネル層上に形成されているゲート絶縁膜、ゲート絶縁膜上に形成されているゲート電極、ゲート電極上に形成されている層間絶縁膜、層間絶縁膜上に形成され、第1導電層と第2導電層を含んでソース電極を有するデータ線、層間絶縁膜上に形成され、第1導電層と第2導電層を含むドレイン電極、ドレイン電極の第1導電層から延長された画素電極、データ線及びドレイン電極上に形成されている保護膜、並びに保護膜上に形成されている間隔材を含む。

(もっと読む)

表示装置

【課題】 アクティブマトリクス型の液晶表示装置の表示品質を向上させる。

【解決手段】 複数本の走査信号線と、前記複数本の走査信号線と立体的に交差する複数本の映像信号線と、マトリクス状に配置された多数個のTFT素子とを有し、前記多数個のTFT素子は、それぞれ、前記複数本の走査信号線のうちの1本にゲートが接続され、前記複数本の映像信号線のうちの1本にドレインまたはソースのいずれか一方が接続されている表示パネルを有する表示装置であって、前記多数個のTFT素子は、前記ゲートが接続されている走査信号線の信号入力端からの距離および前記ドレインまたはソースのいずれか一方が接続されている映像信号線の信号入力端からの距離に応じて、それぞれのTFT素子のチャネル幅またはチャネル長あるいはその両方が異なる表示装置。

(もっと読む)

液晶表示装置

【課題】視野角特性に優れた高品質な液晶表示装置を提供することを課題とする。

【解決手段】第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の抵抗と、第2の抵抗と、第1の液晶素子と、第2の液晶素子とを含む画素を有し、前記第1の液晶素子の画素電極は、前記第1のスイッチを介して信号線に電気的に接続され、前記第1の液晶素子の画素電極は、前記第2のスイッチ及び前記第1の抵抗を介して前記第2の液晶素子の画素電極に電気的に接続され、前記第2の液晶素子の画素電極は、前記第3のスイッチ及び前記第2の抵抗を介してCs線と電気的に接続され、前記第1の液晶素子の共通電極は、前記第2の液晶素子の共通電極と電気的に接続されており、前記信号線に前記画素の階調に応じた電位を入力することにより、視野角特性に優れた高品質な表示を得ることができる。

(もっと読む)

液晶表示装置

【課題】視野角特性に優れた高品質な液晶表示装置を提供することを課題とする。

【解決手段】第1のスイッチと、第2のスイッチと、前記第1のスイッチ及び前記第2のスイッチとは異なるタイミングで制御される第3のスイッチと、第1の抵抗と、第2の抵抗と、第1の液晶素子と、第2の液晶素子とを含む画素を有し、前記第1の液晶素子の画素電極は、前記第1のスイッチを介して信号線に電気的に接続され、前記第1の液晶素子の画素電極は、前記第2のスイッチ及び前記第1の抵抗を介して前記第2の液晶素子の画素電極に電気的に接続され、前記第2の液晶素子の画素電極は、前記第3のスイッチ及び前記第2の抵抗を介してCs線と電気的に接続され、前記第1の液晶素子の共通電極は、前記第2の液晶素子の共通電極と電気的に接続されており、前記信号線に前記画素の階調に応じた電位を入力することにより、視野角特性に優れた高品質な表示を得ることができる。

(もっと読む)

81 - 100 / 130

[ Back to top ]